数字变频的本质是将输入信号与本振信号相乘,从而实现频谱搬移。作为数字信号处理中的关键环节,数字变频广泛应用于接收与发射链路中,并直接影响后续滤波、抽取、插值及解调等处理效果。由于 FPGA 具备较强的并行处理能力和良好的实时性,因此非常适合用于数字变频系统的实现。 1 数字变频原理 如下图所示,左图为输入信号 x(t)的频谱,其中心频率为 f0;右图为本振信号 ej2πfct的频谱,其频率为 fc。 两者在时域相乘后,时域相乘对应频域卷积,所以输入信号频谱会整体搬移 fc,因此混频后信号的中心频率变为 f0+fc。…

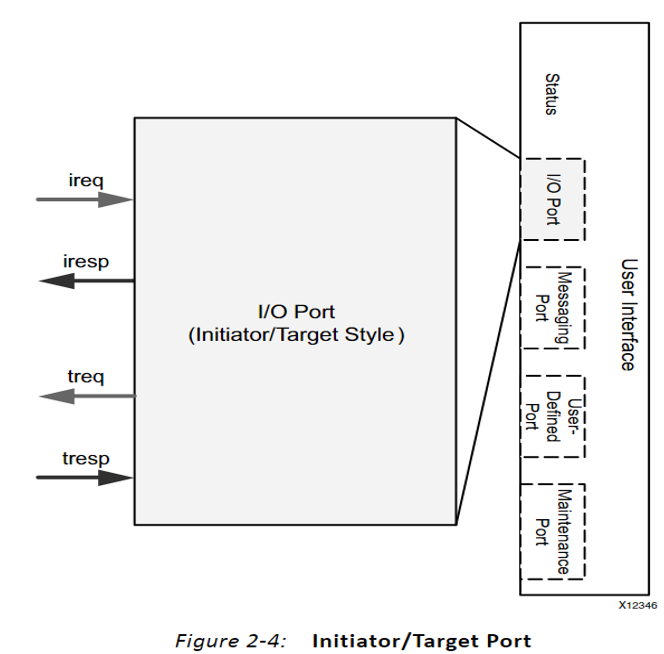

1 背景 在用户使用Xilinx SRIO Gen2 IP时,最关注的就是User Interface。因为用户只需理解User Interface,就能利用SRIO Gen2 IP实现数据的高速传输,而不需要关注RapidIO协议的过多细节。User Interface包含I/O端口集和三个可选端口。其中,任何支持的I/O事务(例如NWRITEs、NWRITE_Rs、SWRITEs、NREADs、RESPONSEs和DOORBELL)都通过I/O端口进行发送或接收。 I/O端口可以配置为两种模式:Condense…