自大学毕业以来,时光在忙碌中悄然流逝。日复一日的工作节奏令人渐感麻木,唯有及时总结,方能清晰地感知这一年的脚步。从某种意义上说,这份总结本身便是一种收获。 1. 工作 今年我换了一次工作。原本的公司在发展壮大的过程中变得愈发封闭,规章制度日益严苛、上下级关系也更加森严,而我对薪资待遇本就不太满意。没想到跳槽后发现,新公司同样“水深”,各种“套路”层出不穷,让我不得不感慨:或许不少国内企业都存在这样的“窝里斗”现象。也许今后我会考虑去外企尝试一下。 这一年里,我主要还是在做接口相关的工作,对数据流的处理越发得心应手,…

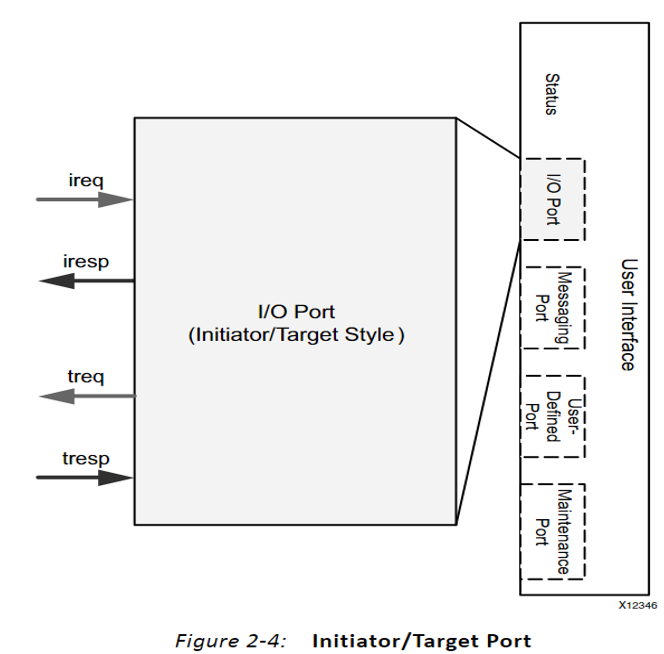

1 背景 在用户使用Xilinx SRIO Gen2 IP时,最关注的就是User Interface。因为用户只需理解User Interface,就能利用SRIO Gen2 IP实现数据的高速传输,而不需要关注RapidIO协议的过多细节。User Interface包含I/O端口集和三个可选端口。其中,任何支持的I/O事务(例如NWRITEs、NWRITE_Rs、SWRITEs、NREADs、RESPONSEs和DOORBELL)都通过I/O端口进行发送或接收。 I/O端口可以配置为两种模式:Condense…

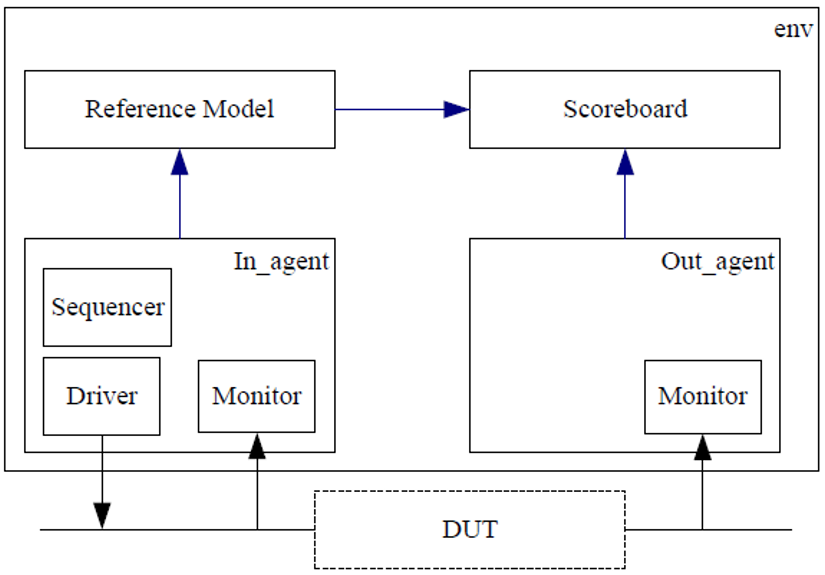

1 背景 如今数字芯片(SoC/ASIC/FPGA)的设计日益复杂,验证工程师的角色也变得越来越重要。有效的验证流程可以在设计初期发现bug,从而显著提升设计的稳定性和正确性。 作为一名FPGA工程师,我发现用Verilog编写的简单testbench已无法满足复杂算法或逻辑的验证需求。Verilog编写的testbench通常非常臃肿且不灵活,不利于代码维护。此外,因为缺乏标准化结构,不同项目通常需要从头搭建验证平台,导致代码难以复用。同时,较差的验证平台结构会增加验证组件之间的耦合,导致对一个组件的修改可能影响…

1 背景 在Xilinx AXI 1G/2.5G Ethernet Subsystem IP中,使用了双通道AXI Stream接口设计,实现了数据流与控制流/状态流的分离。数据流用于传输以太网报文数据,控制流用于传输TX标志信息和校验指示信息,状态流用于传输报文的目的MAC地址和状态等信息。 IP示意图: 2 解析 2.1 TX Stream 如图所示,TX_data的ready信号需要等到TX_control的控制流信息被完全接收后才能拉高。因此,对于每一帧报文,IP必须先接收控制流信息,然后才能接收数据流。 …

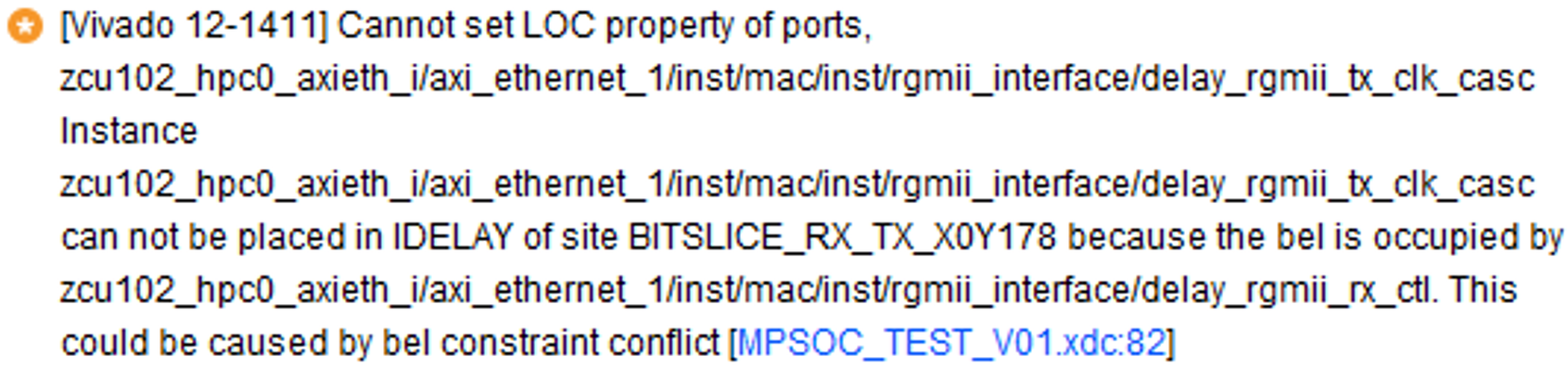

1 背景 在FPGA的高速接口应用中,接口时序常常要求非常严格。因此,经常会利用IOB(I/O Block)中的IODelay资源对端口信号进行延时调整。单个IODelay所能提供的延时是有限的;当需要较长延时时,可以采用IODelay级联以实现更长时间的延时。 2 问题 在以太网工程应用中,为了对输出时钟TXC端口进行延时,采用了ODELAY3和IDELAY3级联。然而,在绑定I/O端口时,遇到了报错。 3 分析 由报错可知,TXC端口所需的IDELAY3的位置(BITSLICE_RX_TX_X0Y178)已被R…

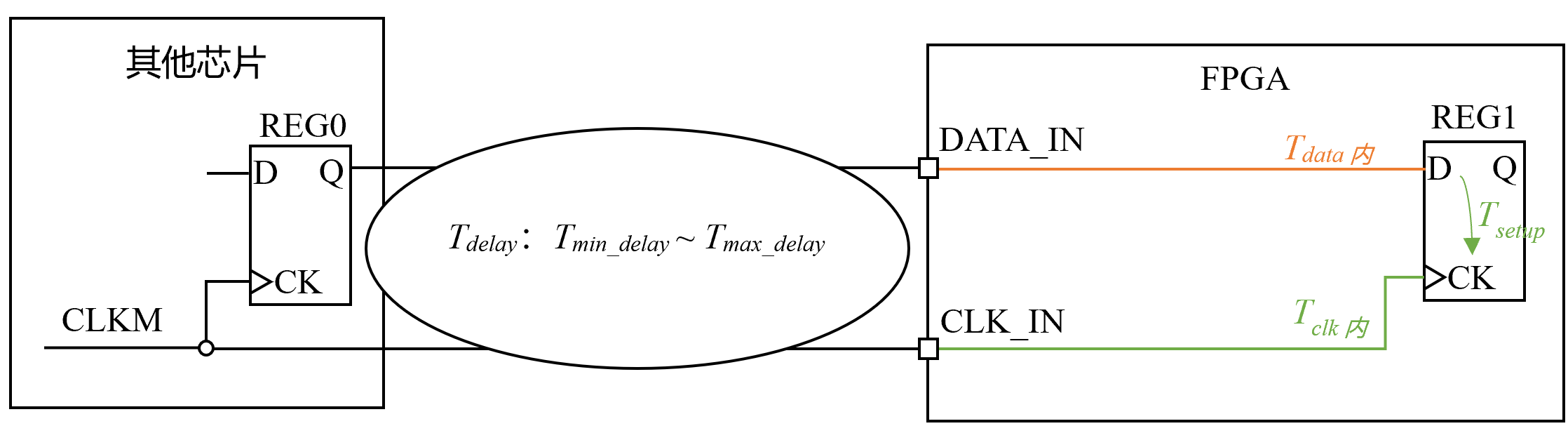

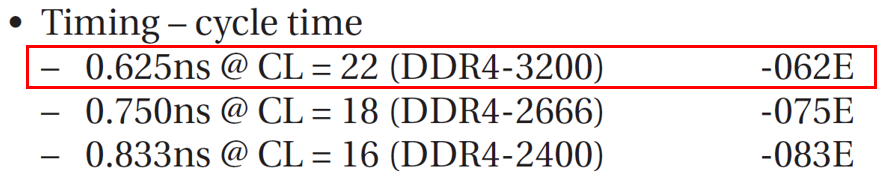

1 背景 使用Zynq平台时,我们往往希望尽量提高PS端程序的运行速度。PS端DDR的数据传输速率对PS端运行速度有显著影响。例如,DDR读写速度慢会减缓处理器在数据读取或写入期间的效率,进而降低整体处理速度。因此,提升PS端DDR的数据传输速率是至关重要的。 2 问题 为了最大限度地提升Zynq MPSoC平台的性能,我们需要深入了解如何配置该平台,以尽量提高DDR的数据传输速率。 3 环境 硬件 主芯片:xczu4ev-sfvc784-2-i;DDR4:MT40A512M16LY-062E 软件 Vivado …

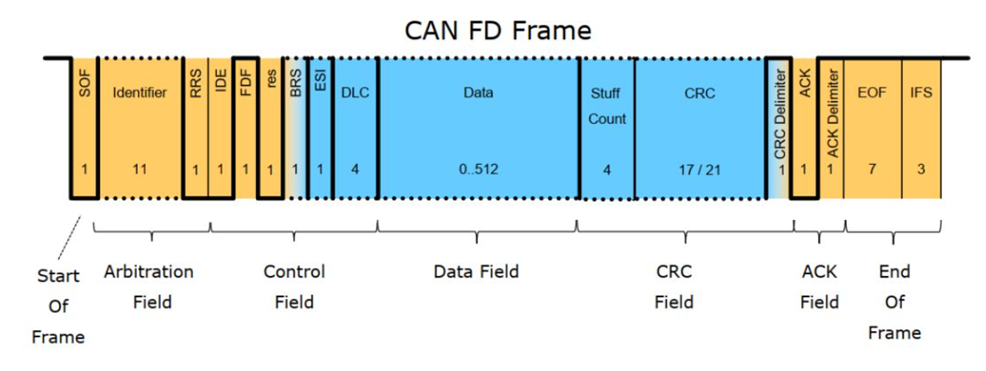

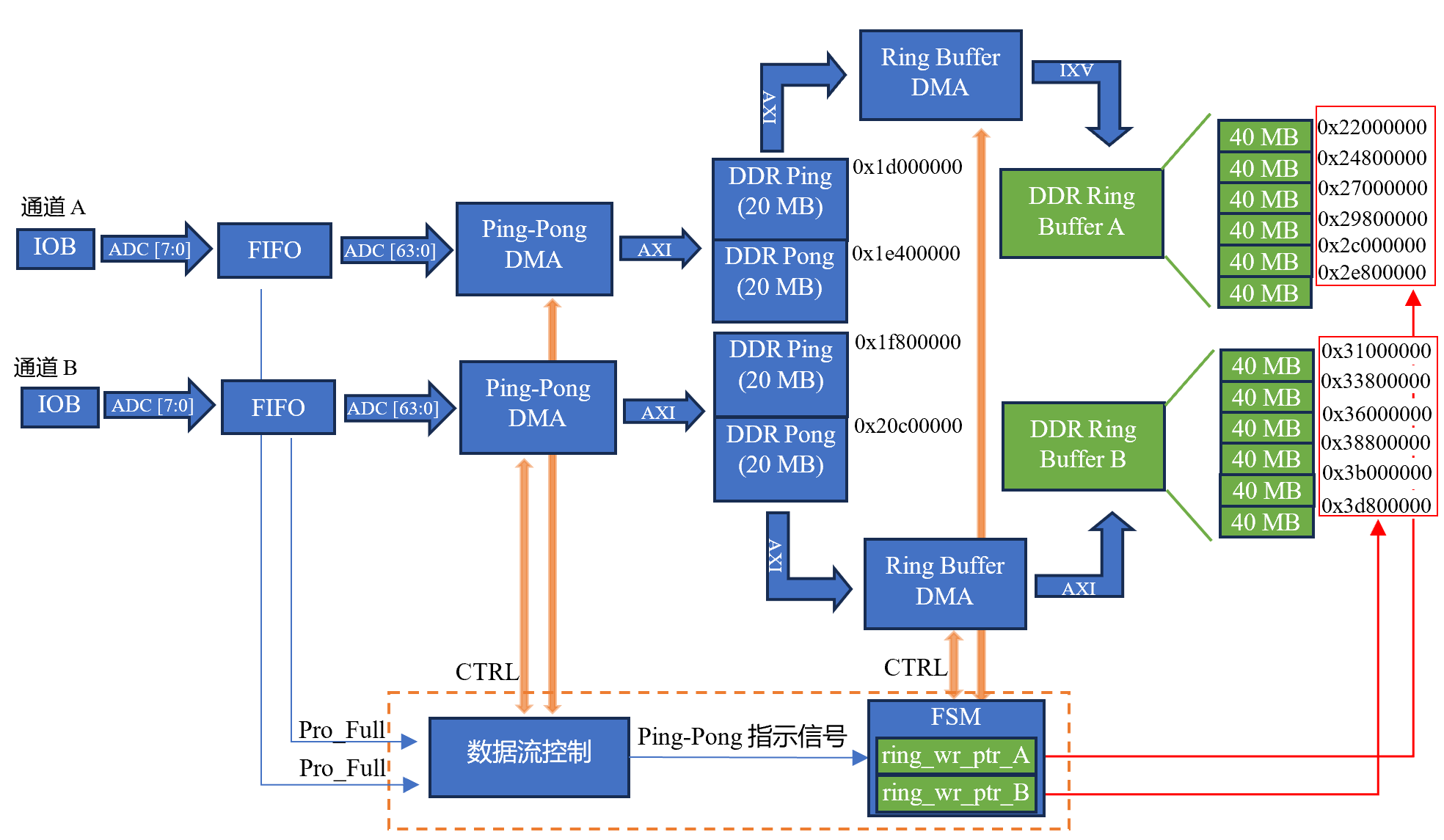

1 需求 1、PL端通过AXI总线将ADC采样得到的每通道40 MB/s的ADC_A和ADC_B两个通道的数据传输至DDR环形缓冲区(Ring Buffer),以便PS端进行读取。 2、提供DDR Ring Buffer的PL写指针,以确保PS端在读取数据时能够避开PL正在写入的DDR地址区域。 2 功能点 1、正确采样每通道40MB/s 的ADC数字信号。 2、将采样得到的ADC数据送入FIFO缓存。 3、将FIFO中的数据搬运到DDR Ping-Pong Buffer缓存。(为将来可能的算法做准备) 4、将DD…