数字变频的本质是将输入信号与本振信号相乘,从而实现频谱搬移。作为数字信号处理中的关键环节,数字变频广泛应用于接收与发射链路中,并直接影响后续滤波、抽取、插值及解调等处理效果。由于 FPGA 具备较强的并行处理能力和良好的实时性,因此非常适合用于数字变频系统的实现。

1 数字变频原理

1 数字变频原理

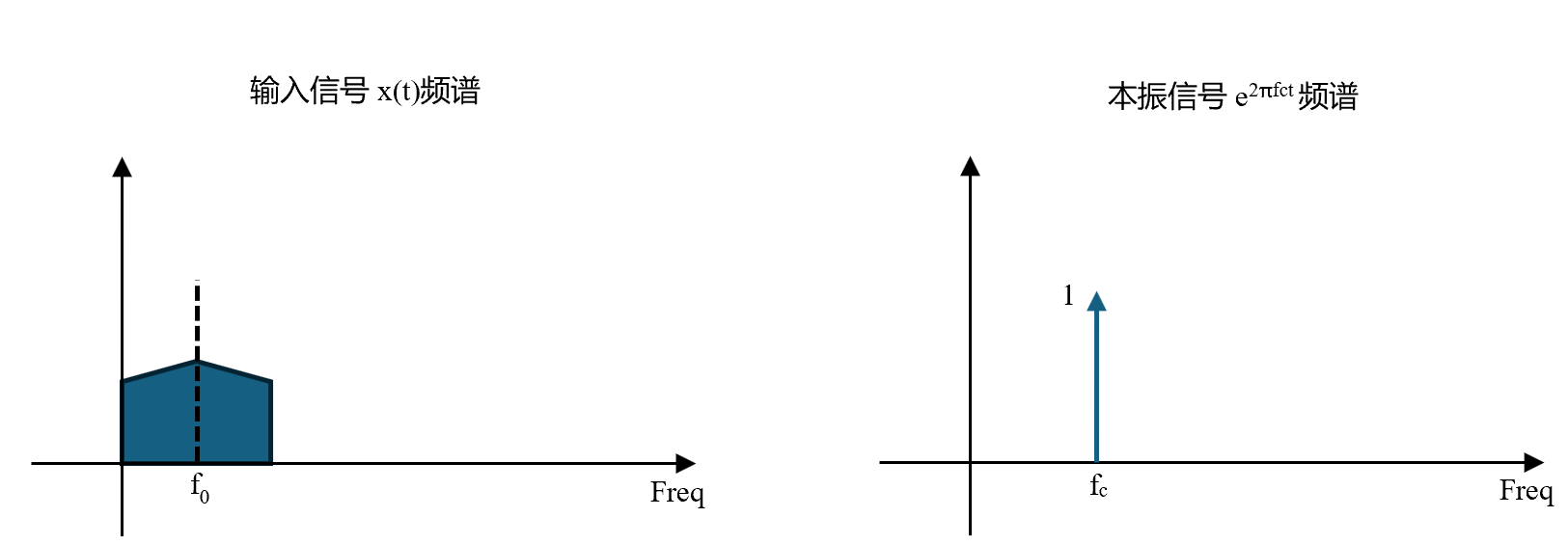

如下图所示,左图为输入信号 x(t)的频谱,其中心频率为 f0;右图为本振信号 ej2πfct的频谱,其频率为 fc。

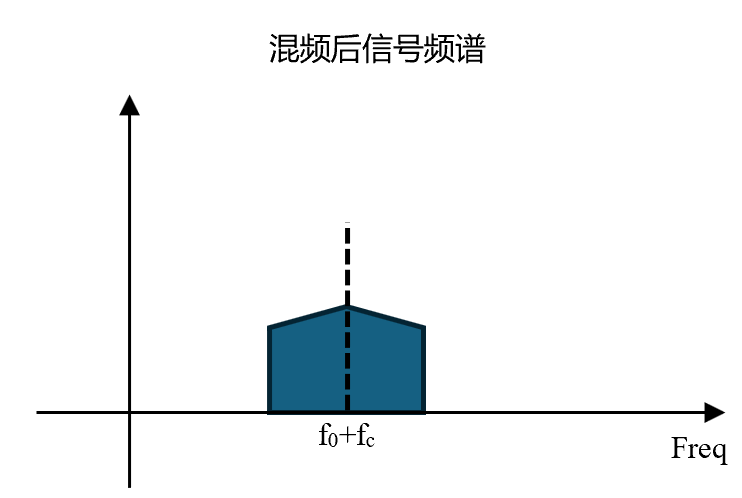

两者在时域相乘后,时域相乘对应频域卷积,所以输入信号频谱会整体搬移 fc,因此混频后信号的中心频率变为 f0+fc。

数字变频的本质是通过输入信号x[n]与复指数本振信号相乘,实现信号频谱的平移,其表达式为:

y[n]=x[n]ej2πfcfsn

其中,fc表示混频本振频率,fs 表示输入信号的采样率。当 fc为正时

,输出频谱相对于输入频谱向高频方向平移;当 fc为负时,输出频谱相对于输入频谱向低频方向平移。

2 FPGA实现数字变频

传统做法一般是先用 DDS IP 核产生本振信号,再用乘法器把输入信号和本振信号相乘完成混频。这种方案比较常见,但缺点是会占用较多 DSP48E1 资源。

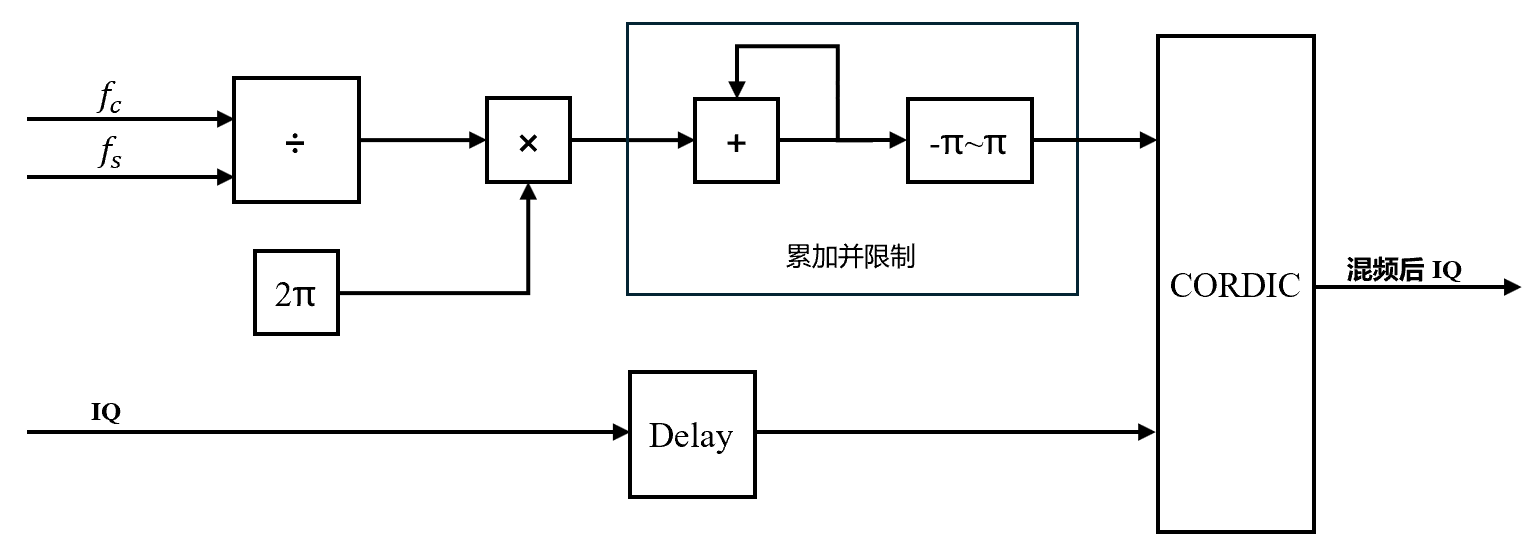

为了减少资源消耗,这里采用一种基于 CORDIC 的实现方法。它利用相位旋转来完成频移,不再完全依赖传统乘法器做混频,因此更适合资源受限或多通道的 FPGA 设计场景。

2.1 FPGA 实现过程

- 根据混频频率 fc和采样率 fs,计算相邻采样点之间的相位增量:Δϕ=2πfcfs

- 对相位增量 Δϕ进行逐点累加,得到本振信号在各个采样时刻对应的相位值。

- 将累加后的相位限制在 [−π,π]范围内,便于后续送入 CORDIC 模块进行旋转运算。

- 将输入 IQ 信号送入 CORDIC 旋转模块,按对应相位进行旋转,输出结果即为完成频率搬移后的混频信号。将输入 IQ 信号作为 CORDIC 旋转模式的输入信号,以当前相位值作为旋转角,对 IQ 信号进行复平面旋转。由于复数乘法在等效为相位旋转,因此 CORDIC 旋转后的输出即为混频后的 IQ 信号。

累加并限制模块的中对相位进行折返处理:当累加结果大于 π时减去 2π,当累加结果小于 −π时加上 2π,从而始终将相位值限制在 [−π,π]范围内。

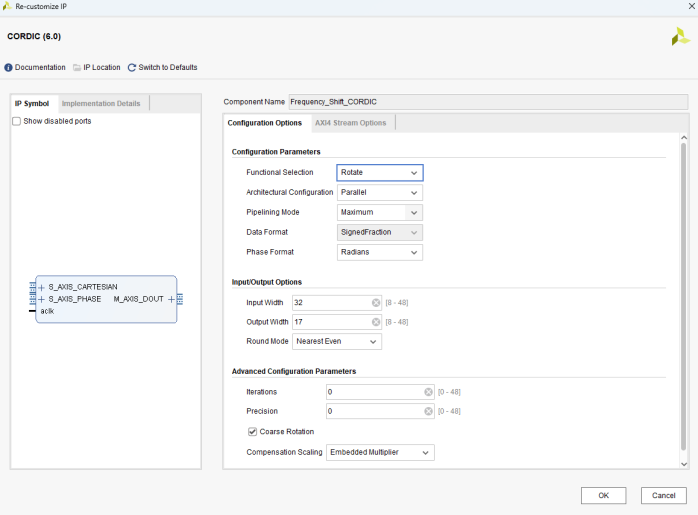

2.2 CORDIC IP配置

Love From China~

Love From China~

文章评论