1 背景

使用Zynq平台时,我们往往希望尽量提高PS端程序的运行速度。PS端DDR的数据传输速率对PS端运行速度有显著影响。例如,DDR读写速度慢会减缓处理器在数据读取或写入期间的效率,进而降低整体处理速度。因此,提升PS端DDR的数据传输速率是至关重要的。

2 问题

为了最大限度地提升Zynq MPSoC平台的性能,我们需要深入了解如何配置该平台,以尽量提高DDR的数据传输速率。

3 环境

硬件

主芯片:xczu4ev-sfvc784-2-i;DDR4:MT40A512M16LY-062E

软件

Vivado 2018.3

4 分析

DDR的数据传输速率取决于两个因素:1、DDR本身能支持的速率。2、MPSoC PS端DDR控制器能支持的速率。

4.1 DDR速率

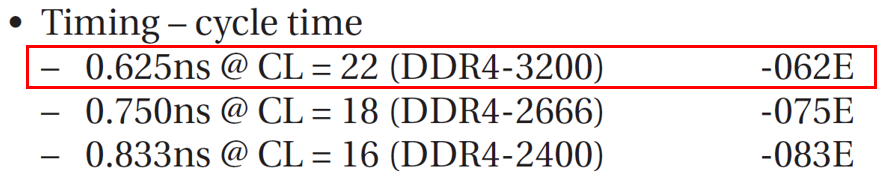

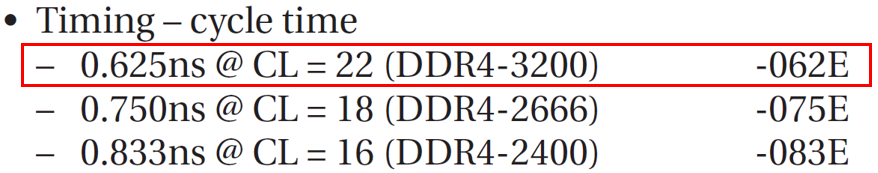

根据DDR芯片数据手册,-062E型号的DDR时钟最小周期为0.625 ns,这意味着DDR时钟频率为1600 MHz,相应的DDR支持的最高数据传输速率为3200 MT/s (Mega-transfer per second)。

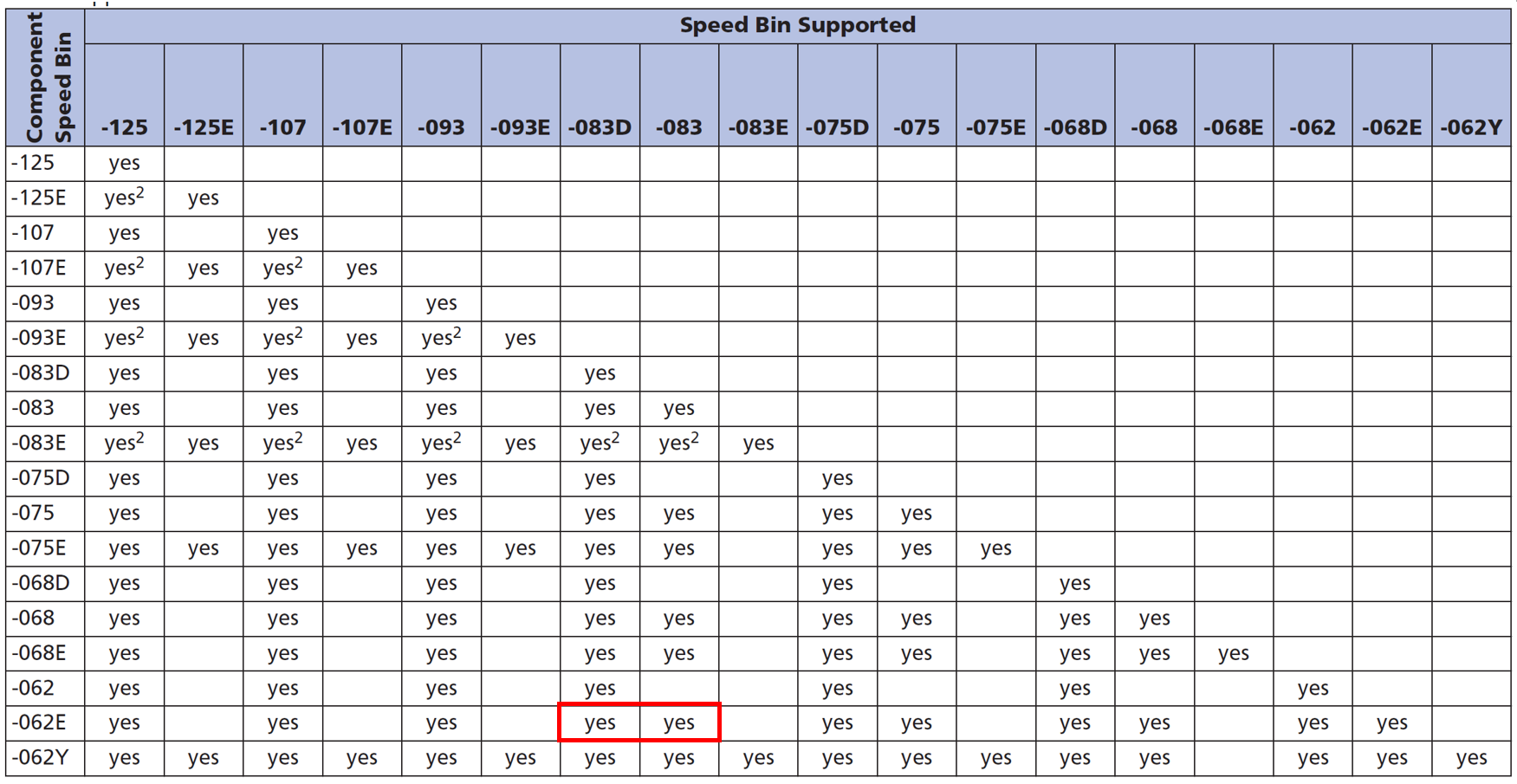

根据DDR4的手册,-62E速度型号的DDR4兼容-083和-083D型号。

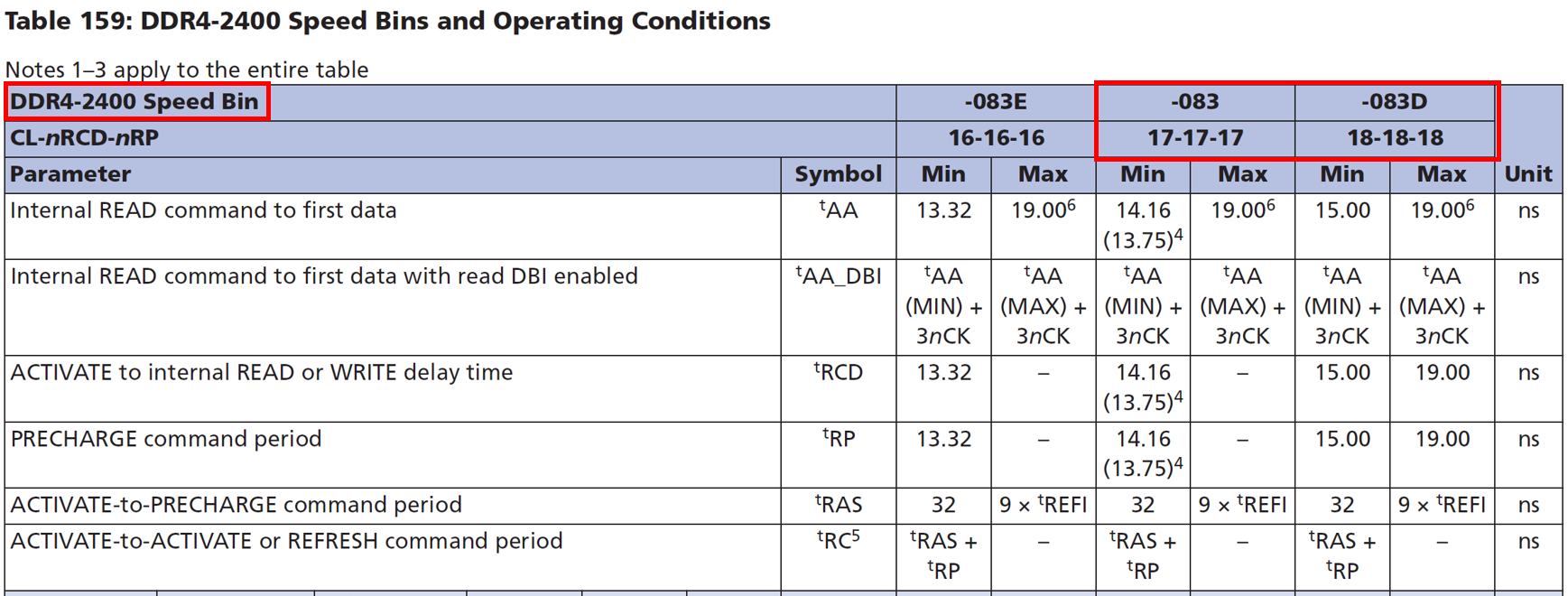

-083和-083D均对应DDR4-2400速度等级。其中,-083对应的是DDR4-2400(17-17-17),而-083D对应的是DDR4-2400(18-18-18)。

4.2 DDR控制器速率

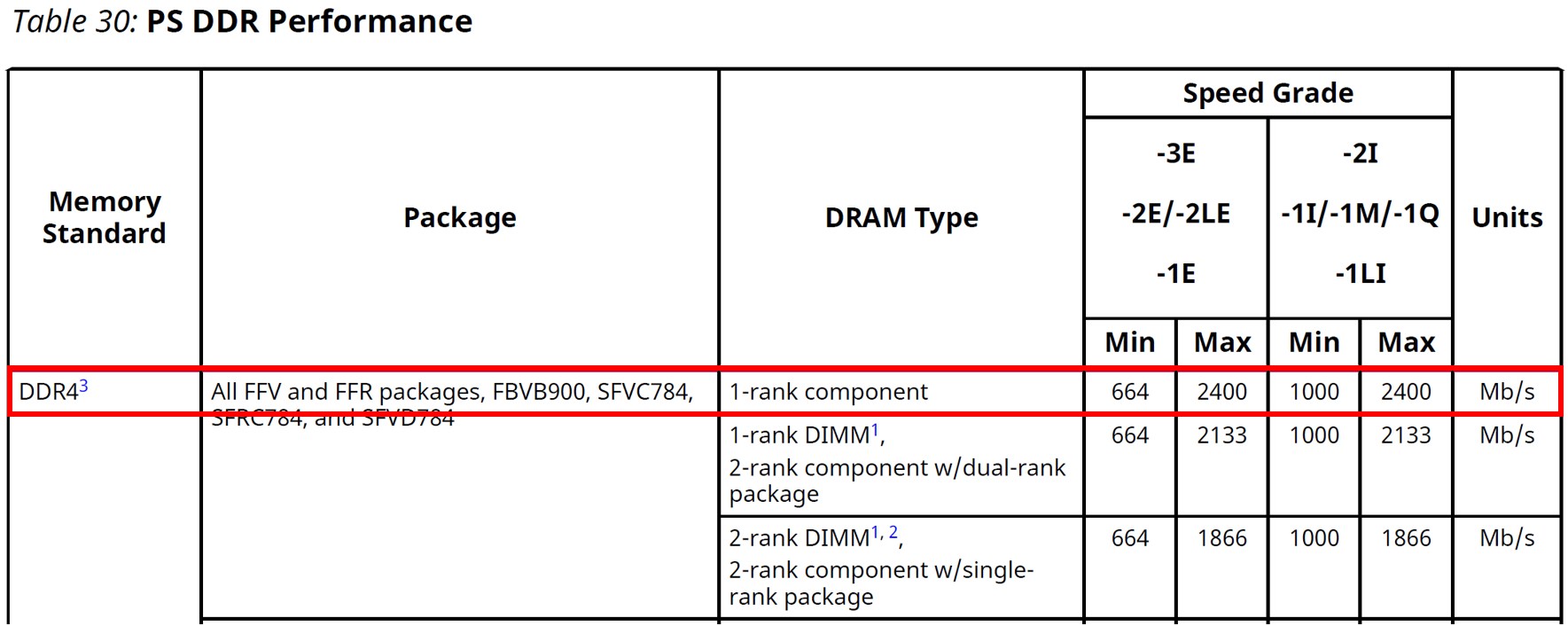

根据手册【DS925】,MPSoC的单根DDR数据线速率最高支持2400 Mb/s,即支持的DDR的最高数据传输速率为2400 MT/s。

4.3 小结

虽然-62E型号DDR支持最高3200 MT/s的数据传输速率,但MPSoC的DDR控制器最高仅支持2400 MT/s。因此,-62E型号DDR需降速至2400 MT/s以匹配控制器。-62E型号可选择兼容的速度型号-083和-083D,以实现降至2400 MT/s速率的使用。

5 配置流程

5.1 时钟配置

5.1.1 输入时钟

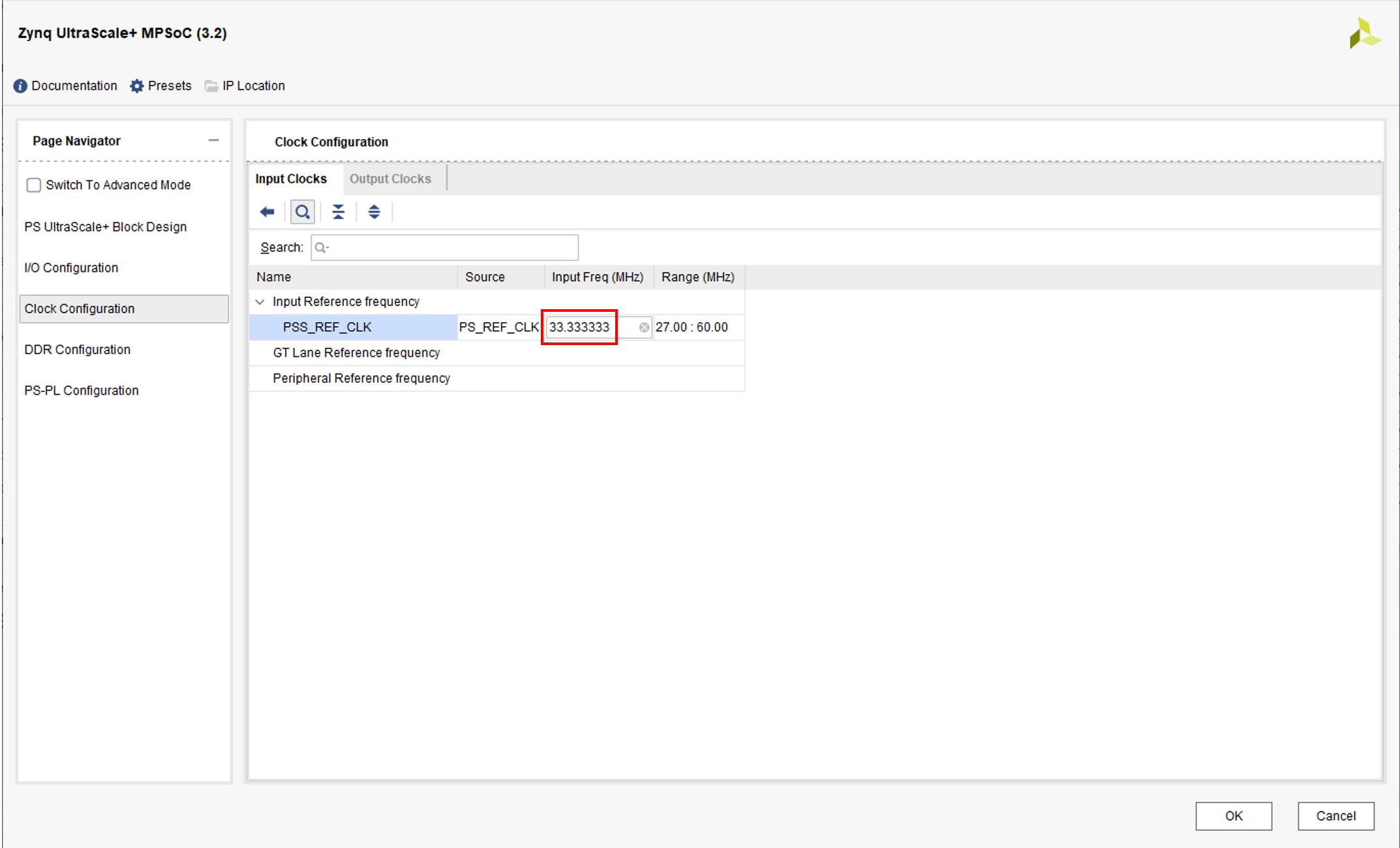

根据原理图,PS端输入的参考时钟源频率为33.333333 MHz。

5.1.2 PLL 输出时钟

1、配置5个系统PLL

原理:

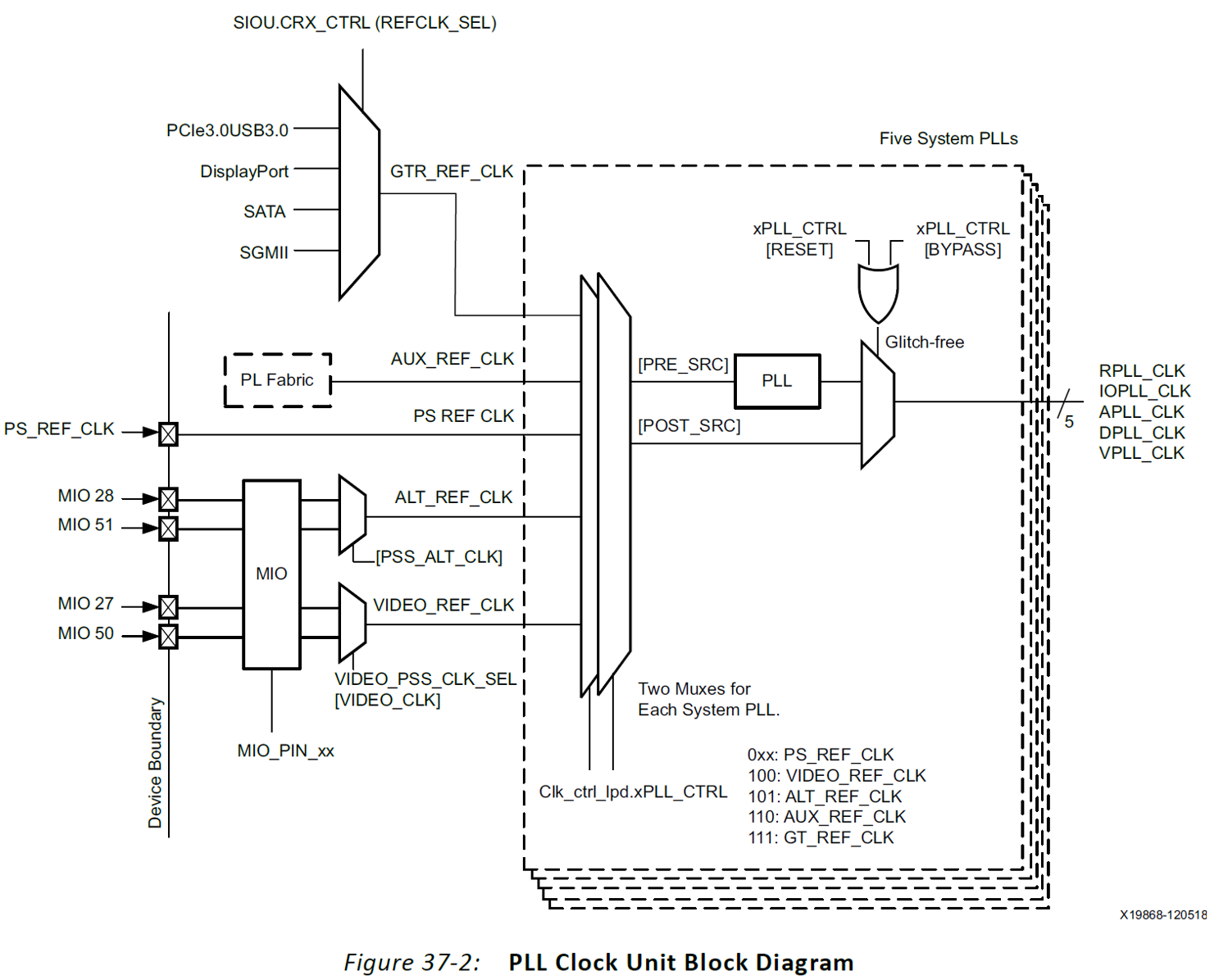

PS端的时钟系统通过五个锁相环单元产生时钟,供处理器、外设、互连结构及其他系统单元使用。每个锁相环单元的架构如上图所示。

其中APLL,DPLL 和 VPLL这三个锁相环在芯片全功耗域(FPD)中。而IOPLL和RPLL在芯片低功耗域(LPD)中。

- 低功耗域

-

- IOPLL(I/O PLL):为所有低速外设和部分互连结构提供时钟

- RPLL(RPU PLL):为 RPU 内核和部分互连结构提供时钟

- 全功耗域

- APLL(APU PLL):为 APU 内核和部分互连结构提供时钟

- VPLL(Video PLL):为 video I/O 提供时钟

- DPLL(DDR PLL):为 DDR 控制器和部分互连结构提供时钟

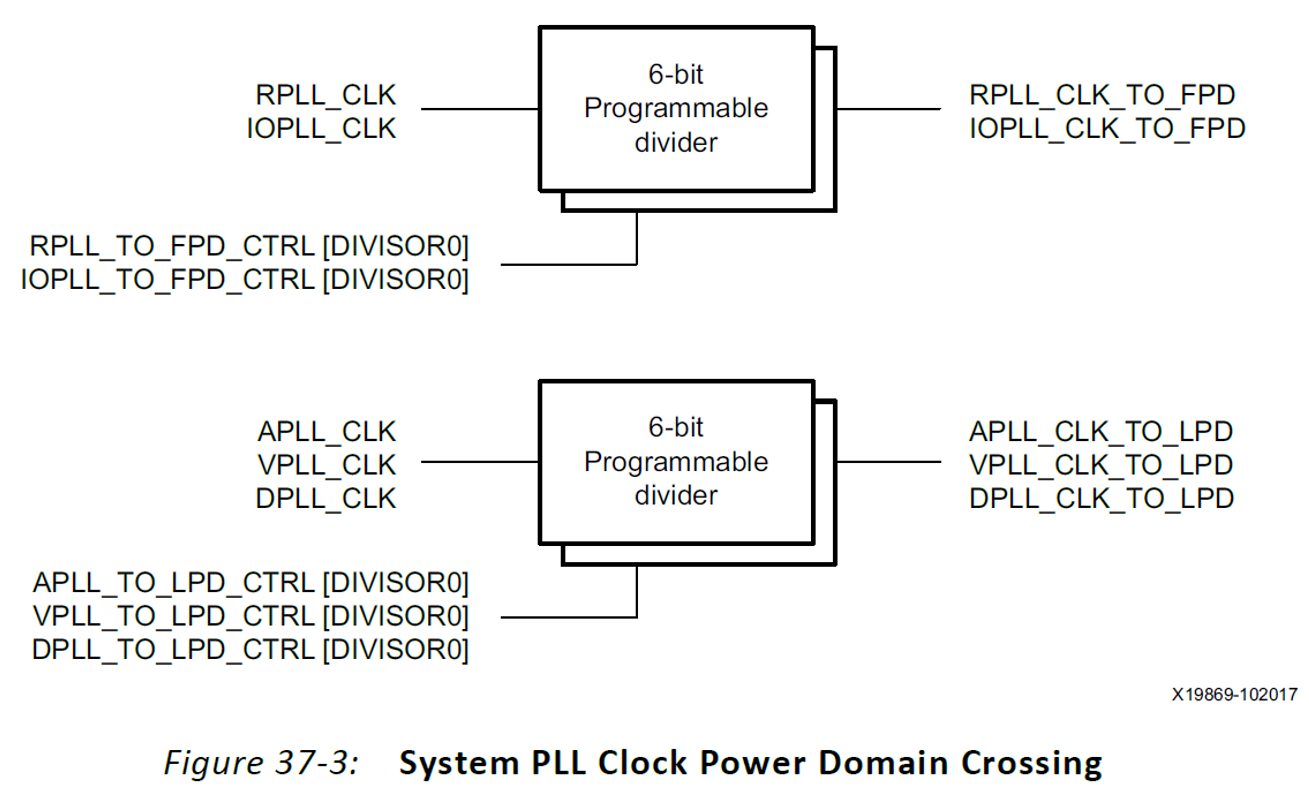

每个锁相环的输出端配备了两个时钟分频器:一个位于锁相环所在的原始功率域,另一个位于不同的功率域中。

Vivado配置:

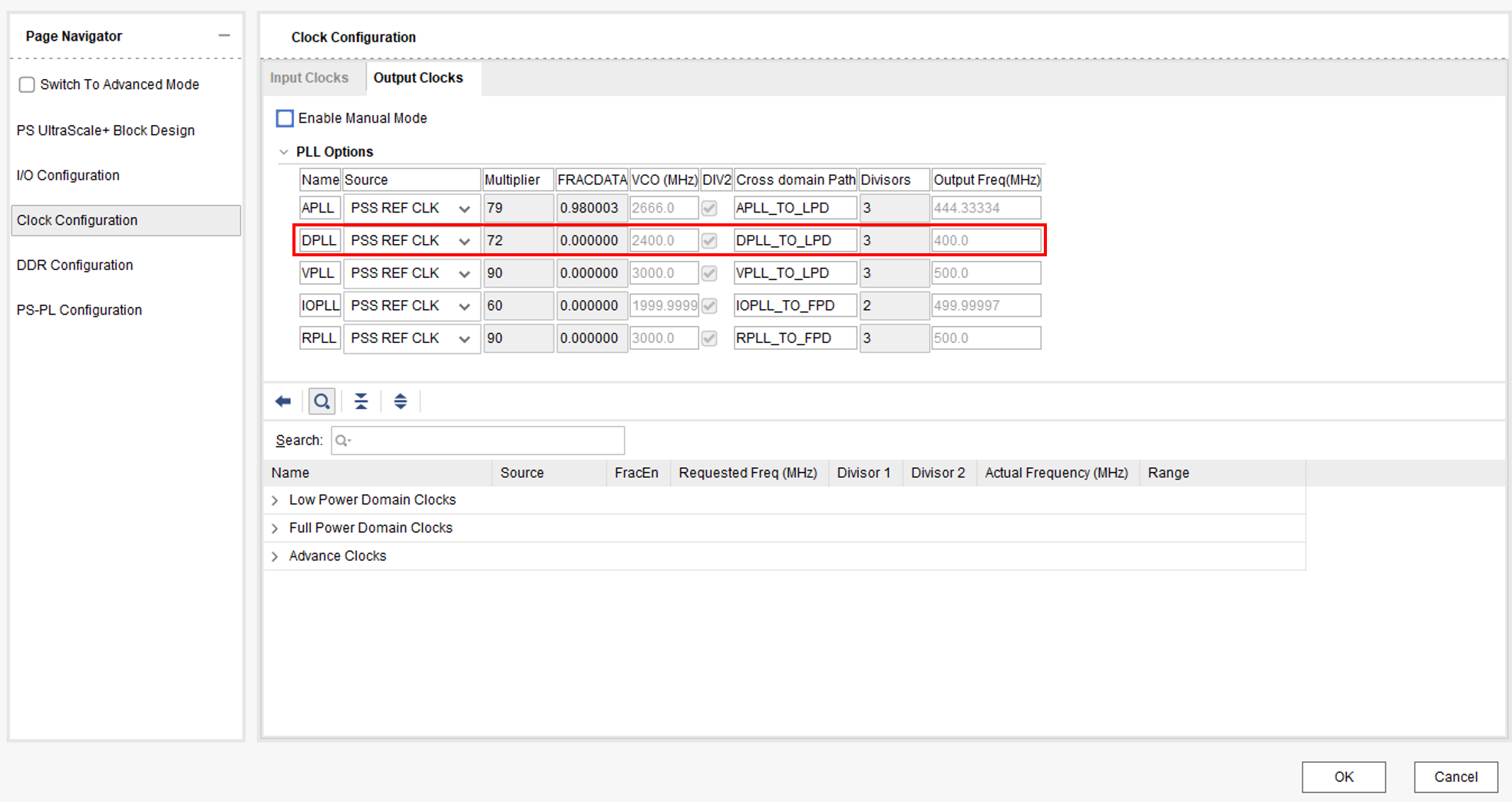

• Source:为锁相环提供的参考时钟源。DPLL锁相环的参考时钟源为PSS REF CLK。

• Multiplier:提供一个6bit整数值作为锁相环压控震荡器(VCO)的输出输出频率相对于参考时钟源频率的倍数。例如,图中DPLL的Multiplier参数设置为72,意味着DPLL的VCO输出时钟频率是PSS REF CLK频率的72倍。

• VCO:其值VCO (MHz) = Multiplier × Source (MHz),代表锁相环通过压控震荡器倍频后的输出频率。例如,图中DPLL的Multiplier为72,Source频率为33.333333 MHz,因此VCO的值为72 × 33.333333 = 2400 MHz。

• DIV2:DIV2使能后,每个PLL的输出频率是VCO输出频率的一半。例如,图中DPLL的DIV2被使能,那么DPLL的最终输出频率为1200 MHz。

• Cross domain Path:指示跨功耗区域的路径。例如,“DPLL_TO_LPD”指的就是在全功耗域(FPD)的DPLL锁相环跨功耗域给低功耗域(LPD)提供时钟。

• Divisors:6-bit分频器,对每个PLL提供的跨功耗域时钟进行整数分频。例如,图中DPLL的Divisors值为3,表示表示DPLL提供给低功耗域(LPD)的时钟经过3分频后输出。

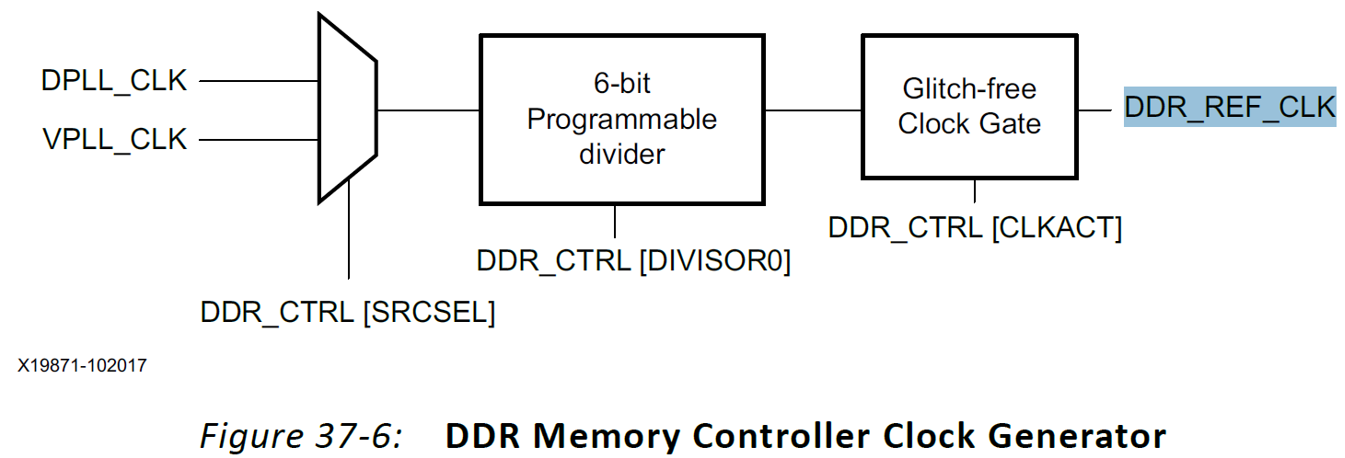

2、DDR控制器时钟

原理:

如图, DPLL_CLK时钟经过一个6-bit分频器分频后,产生的输出时钟DDR_REF_CLK被送往DDR控制器,并作为DDR控制器逻辑的工作时钟。

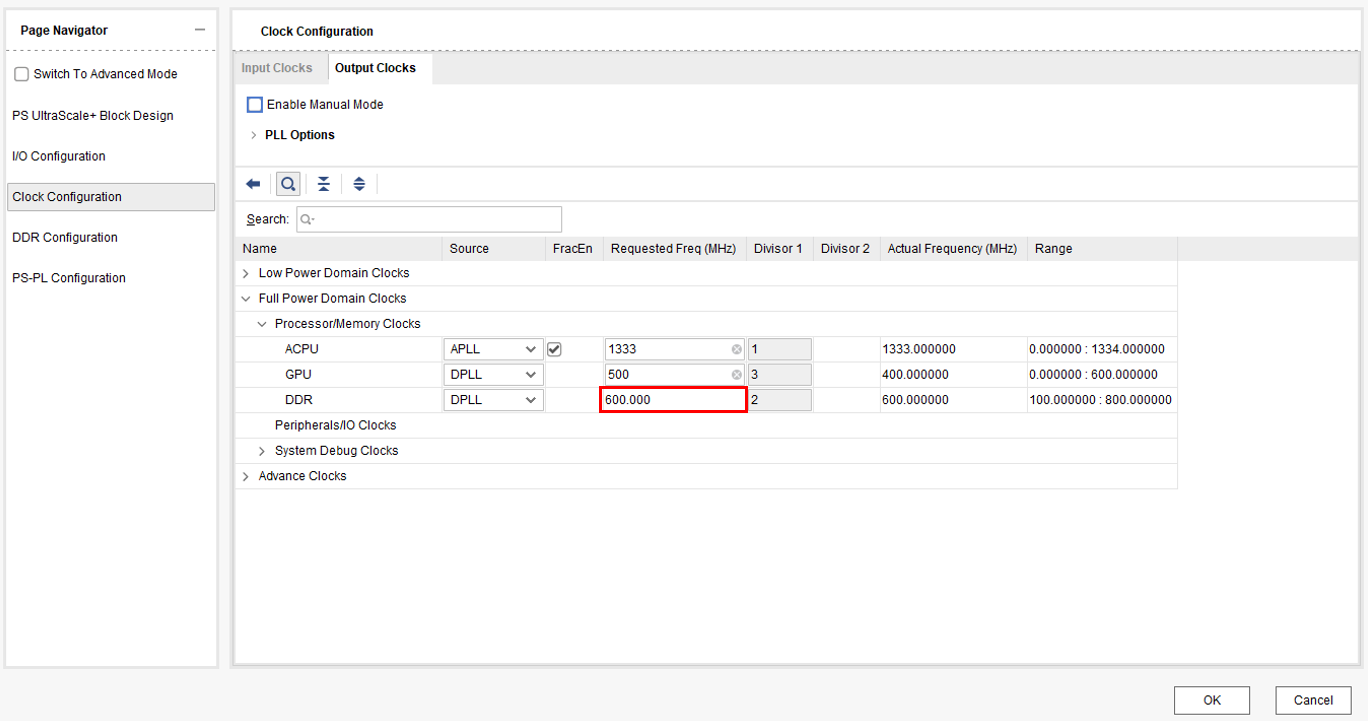

Vivado配置:

这里 DDR 的时钟代表DDR控制器逻辑工作的时钟,是通过 DDR 配置自动生成的。用户不用也无法修改。

5.2 DDR配置

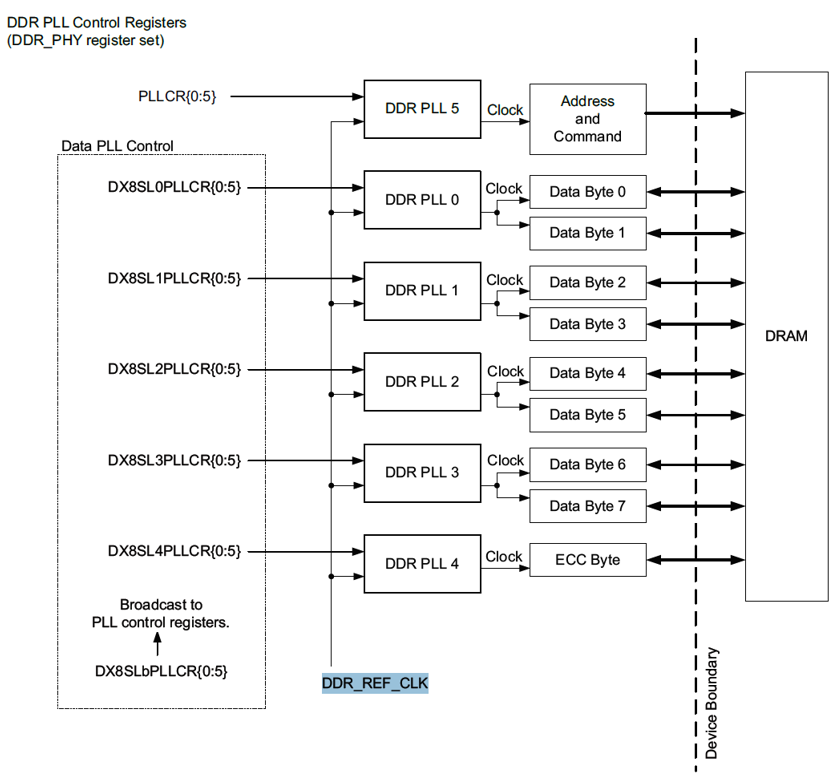

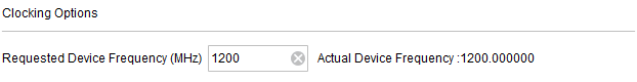

1、Clocking Options

如图,DDR_REF_CLK时钟输入DDR PHY的6个PLL,这些PLL输出的时钟随后被用作DDR接口的驱动时钟。

在Clocking Options中设置的时钟为DDR4接口的驱动时钟。DDR4的数据传输速率为2400 MT/s,采用双边沿数据传输方式。因此,DDR4的驱动时钟频率应为数据传输速率的一半,即1200 MHz。注意,此处的时钟频率只能为DPLL输出时钟的整数倍分频。

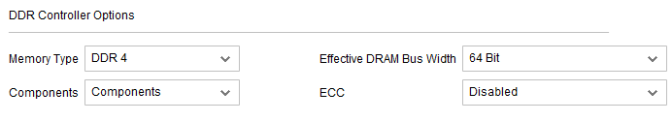

2、DDR Controller Options

- Memory Type:使用的DDR内存种类。

- Components:控制器支持的元件种类。硬件上直接用 DDR 芯片,所以选择 components。

- Effective DRAM Bus Width:DDR接口的数据位宽。若使用4片16-bit的DDR进行组合,则DDR的数据位宽为4 × 16 = 64 bits。

- ECC:使能错误纠正码。

3、DDR Memory Options

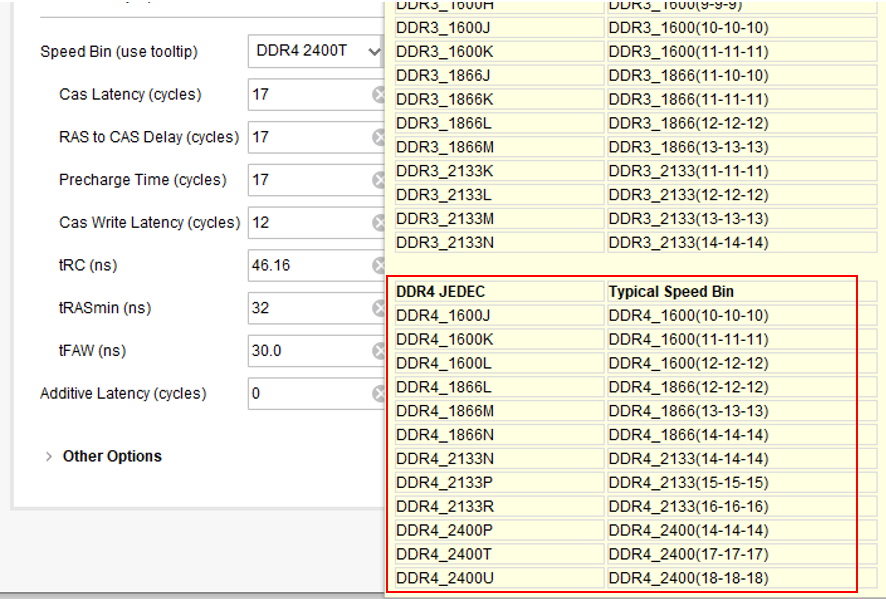

- Speed Bin:DDR使用的速度等级(JEDEC Standard 定义)。

将鼠标悬停在Speed Bin选项上,可以查看DDR控制器支持的DDR4速度等级。例如,Speed Bin DDR4 2400T对应的DDR4速度等级是DDR-2400 (17-17-17)。所选择的DDR控制器的Speed Bin必须与实际使用的DDR4兼容。例如,本文中使用的DDR4速度型号为-64E,与-83速度型号兼容。-83速度型号对应的速度等级是DDR-2400(17-17-17),因此,本文中DDR控制器的Speed Bin选择为DDR4 2400T。

- Cas Latency:DDR读命令到第一个数据读出所需的时钟周期数。这个参数可以根据DDR的速度等级来确定。例如,如果DDR4使用的速度等级为DDR-2400 (17-17-17),其中17-17-17代表CL-nRCD-nRP。CL即Cas Latency,因此在这个例子中,Cas Latency的值应设置为17。

- RAS to CAS Delay:DDR在读写命令之前必须要激活对应bank中对应的行,RAS to CAS Delay代表的就是激活所需的时间。这个参数可以根据DDR的速度等级来确定。例如,速度等级为DDR-2400 (17-17-17) 时,RAS to CAS Delay的值为17。

- Precharge Time:DDR在完成一行数据的读写后,要进行下一行读写之前需要预充电。Precharge Time就是所需的预充电时间。这个参数可以根据DDR的速度等级来确定。例如,速度等级为DDR-2400 (17-17-17) 时,Precharge Time的值为17。

- Cas Write Latency:DDR写命令到第一个数据写入所需的时钟周期数。根据数据手册,DDR-2400 速度等级的DDR4的Cas Write Latency为12

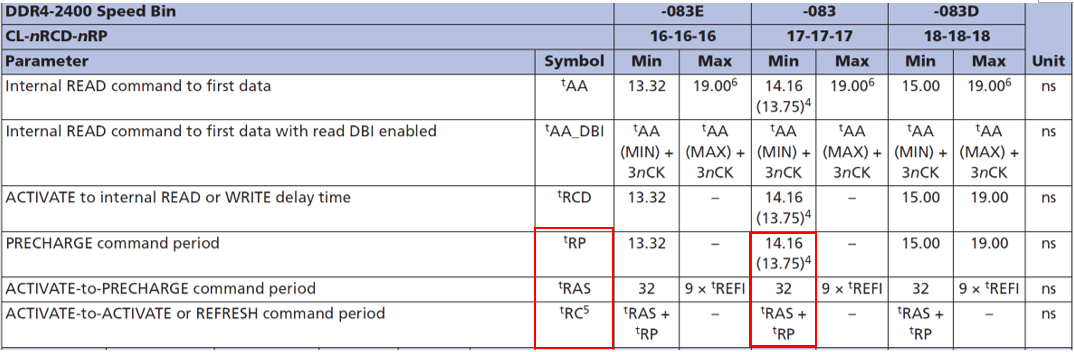

- tRAS and tRC:

如图,根据数据手册,速度型号为-83的DDR4 tRAS = 32 ns;tRC = 46.16ns。

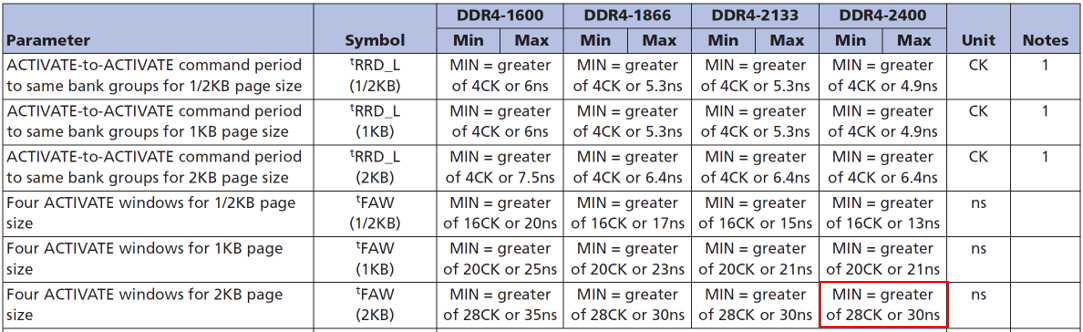

- tFAW:执行4个激活命令所需要的窗口时间。

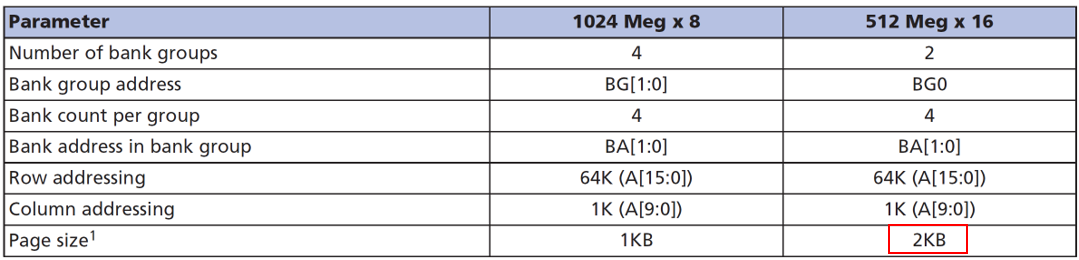

使用的芯片的page size为2KB

根据数据手册,在DDR4使用DDR4-2400的速度等级且一页大小为2KB时,tFAW的最小值为30 ns。为了实现DDR性能的最优化,tFAW的值可以直接配置为这个最小值,即30 ns。

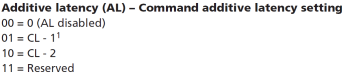

- Additive Latency:附加延迟。使用Post CAS技术时,总线上发出CAS信号(读写/命令)后到这个指令实际被执行的延时。

根据数据手册AL可以为CL – 1 = 16或者CL – 2 = 15,这里选择AL为16.

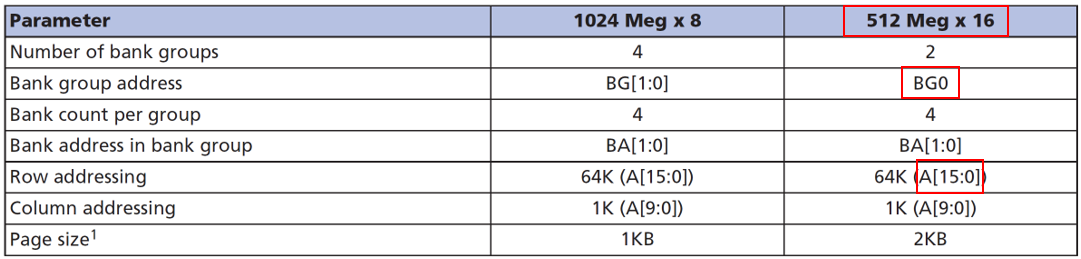

- DRAM IC Bus Width:单个 DRAM 元件的数据位宽。我们用的DDR4单片数据位宽为16 Bits。

- Device Capacity:单个 DRAM 元件的容量。我们用的DDR4容量 = 512Meg x 16 Bits = 8192 MBits。

- Bank Group Address Count:BG的位宽。512Meg x 16 是 BG0,因此为1。

- Row Address Count:RA的位宽。512Meg x 16 是 A[15:0],因此为16。

6 测试

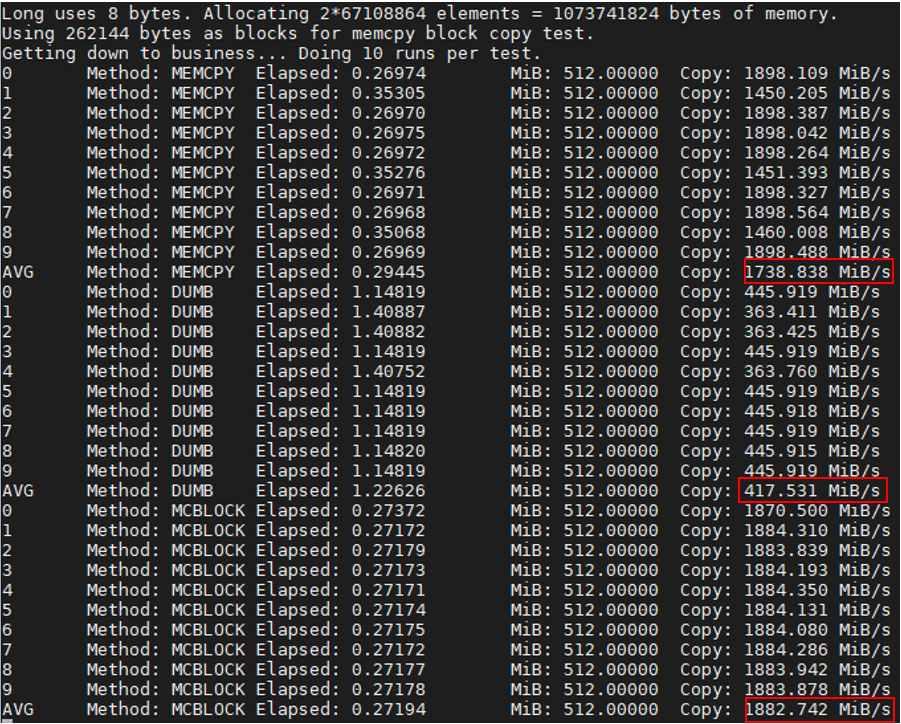

使用裸机代码测试DDR速率:https://github.com/Yong12315/MPSOC-DDR-TEST

.

.

Love From China~

Love From China~

文章评论