1 背景

在FPGA的高速接口应用中,接口时序常常要求非常严格。因此,经常会利用IOB(I/O Block)中的IODelay资源对端口信号进行延时调整。单个IODelay所能提供的延时是有限的;当需要较长延时时,可以采用IODelay级联以实现更长时间的延时。

2 问题

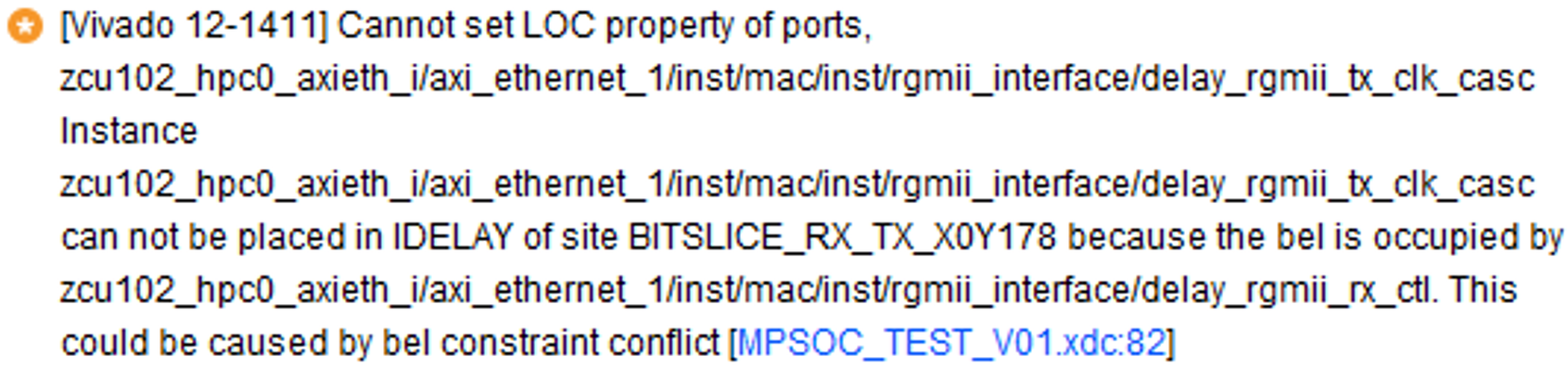

在以太网工程应用中,为了对输出时钟TXC端口进行延时,采用了ODELAY3和IDELAY3级联。然而,在绑定I/O端口时,遇到了报错。

3 分析

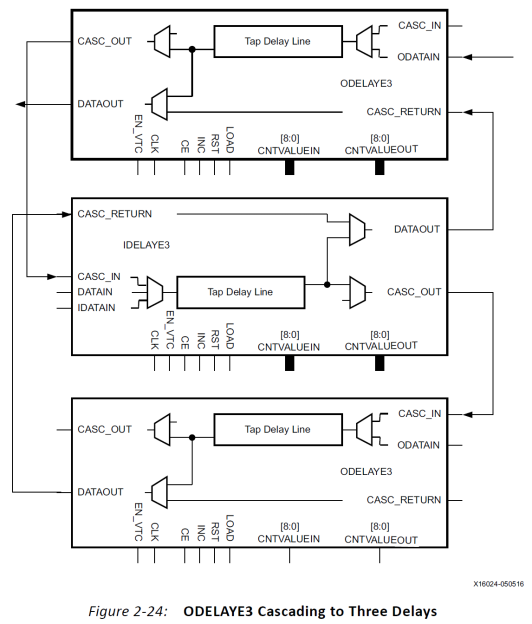

由报错可知,TXC端口所需的IDELAY3的位置(BITSLICE_RX_TX_X0Y178)已被RX_CTL占用。为了避免此类冲突,接下来将详细解析在使用IODelay级联时需要注意的事项。

3.1 理论分析

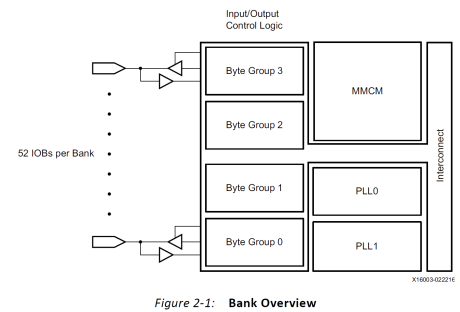

如图,每个I/O Bank可以分为四个Byte组。

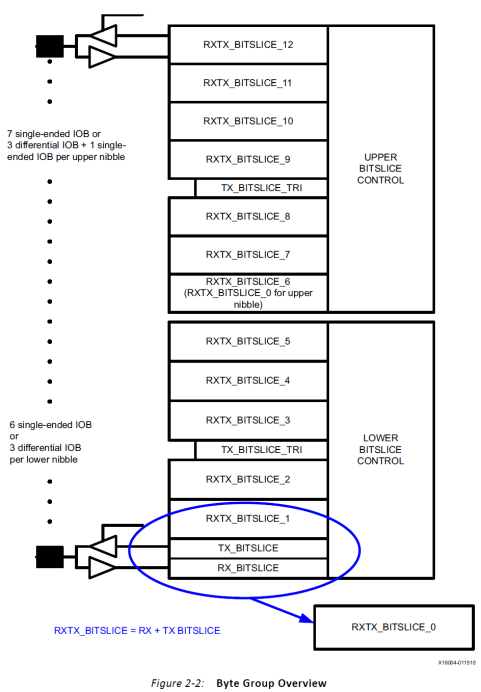

每个Byte组包含13个I/O 端口,每个I/O端口对应了一个RXTX_BITSLICE。

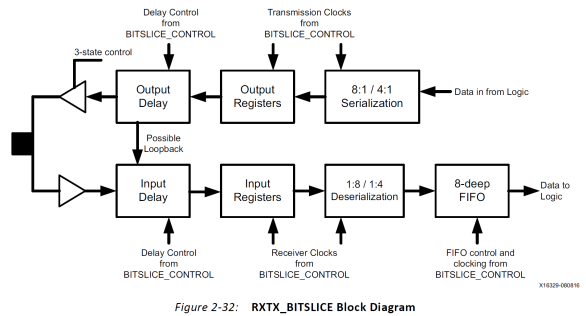

如图所示,每个RXTX_BITSLICE中都包含了IODelay资源。如果I/O端口需要使用IODelay来调整延时,则I/O信号必须经过对应的RXTX_BITSLICE。

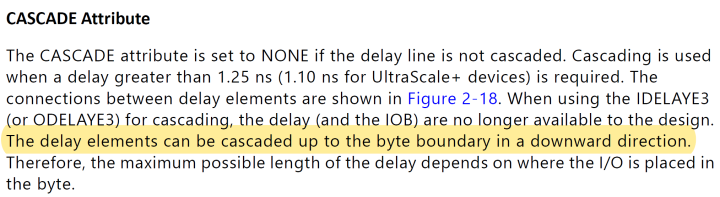

当所需延时超过1.1ns(Ultra Scale+ device)时,需要采用IODelay的级联模式。IODelay级联的要求包括:

在IODelay级联时,IODelay之间的连接使用的是专用的高速布线。

3.2 示例分析

在以太网工程应用中, TXC端口采用了ODELAY3和IDELAY3的级联方式。其中,ODELAY3必须使用与TXC绑定的I/O端口相对应的ODELAY3。

根据IODelay级联的要求,级联的IDELAY3必须满足以下两个条件:

综上,对于需要使用IODelay级联的TXC来说,其绑定的I/O端口有三个要求:

4 问题解决

由报错可知,当前需要使用IODelay级联的TXC端口不满足“IO端口对应的ODELAY3下方的IDELAY3未被占用”的要求。为了解决I/O端口上的冲突,存在两种可能的解决方案:

1. 改变RX_CTL端口的位置,将IDELAY3的位置(BITSLICE_RX_TX_X0Y178)让出来,以便TXC端口使用。

2. 改变TXC端口的位置,使其移到能满足IODelay级联要求的另一个I/O端口。

4.1 修改TXC端口位置前

当前,TXC端口对应的ODELAY3位于BITSLICE_RX_TX_X0Y179,而其下方的IDELAY3位置(BITSLICE_RX_TX_X0Y178)已被RX_CTL占用,导致I/O端口出现冲突。

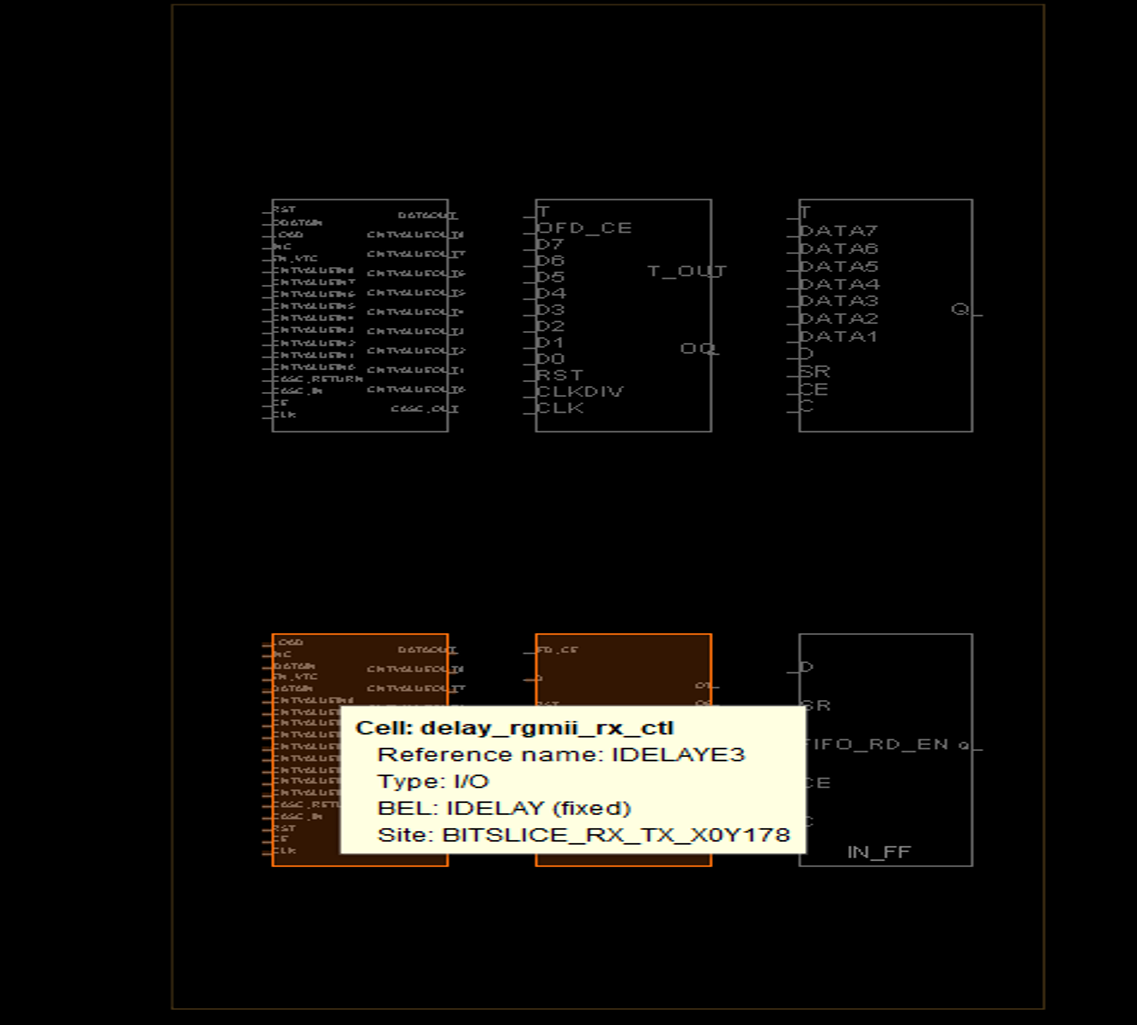

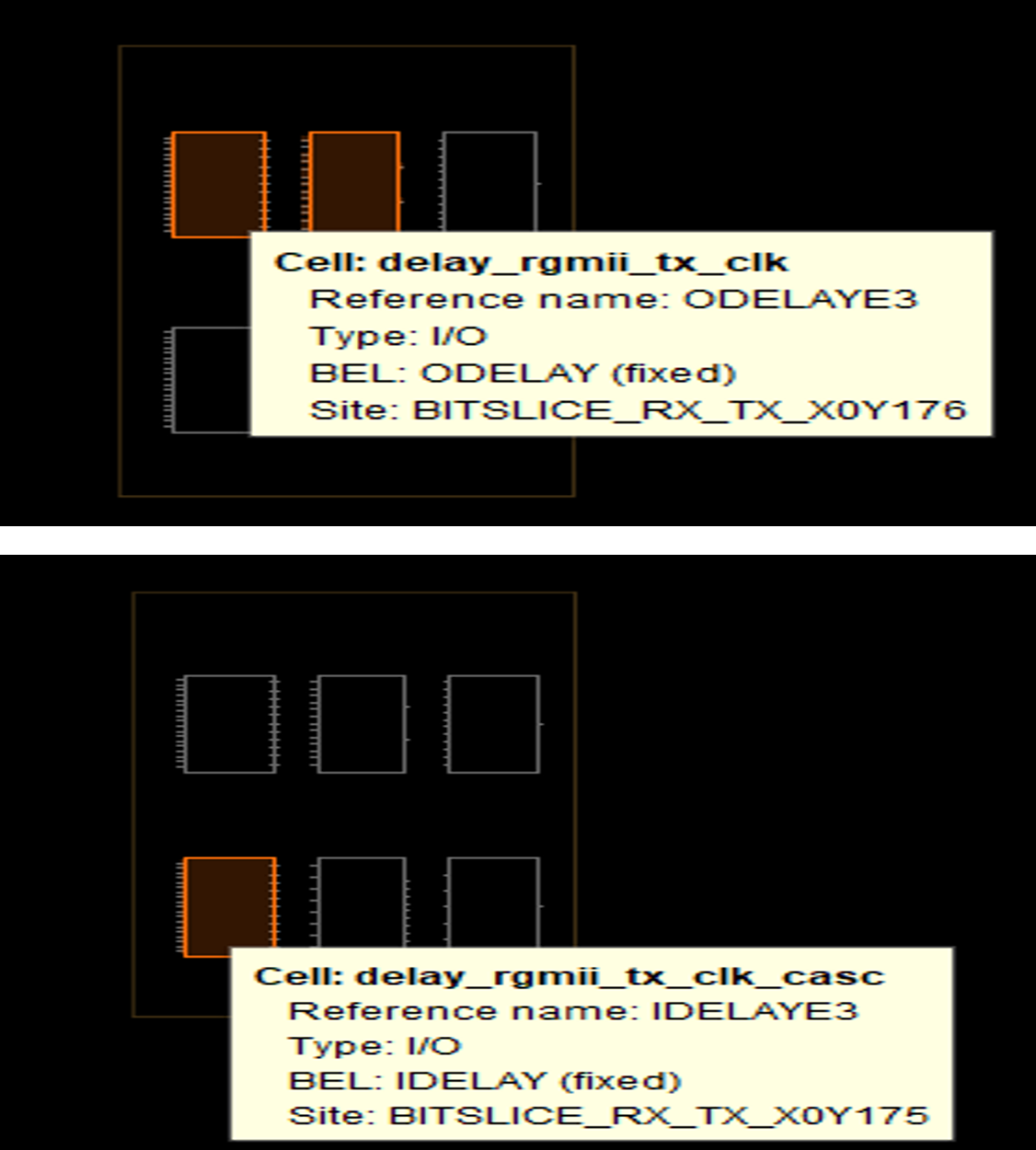

4.2 修改TXC端口位置后

现在,TXC端口对应的ODELAY3位于BITSLICE_RX_TX_X0Y176,其下方的IDELAY3位置(BITSLICE_RX_TX_X0Y175)能够用于级联使用,因此I/O端口不会出现冲突。

5 Reference

1. ug571-ultrascale-selectio

Love From China~

Love From China~

文章评论