1 背景

如今数字芯片(SoC/ASIC/FPGA)的设计日益复杂,验证工程师的角色也变得越来越重要。有效的验证流程可以在设计初期发现bug,从而显著提升设计的稳定性和正确性。

作为一名FPGA工程师,我发现用Verilog编写的简单testbench已无法满足复杂算法或逻辑的验证需求。Verilog编写的testbench通常非常臃肿且不灵活,不利于代码维护。此外,因为缺乏标准化结构,不同项目通常需要从头搭建验证平台,导致代码难以复用。同时,较差的验证平台结构会增加验证组件之间的耦合,导致对一个组件的修改可能影响到验证平台的其他部分。

相比之下,SystemVerilog引入了面向对象的编程特性,允许同一验证组件在不同项目中通过适当配置或扩展来重用。此外,基于SystemVerilog的验证方法学提供了一套类库,使工程师可以非常方便地利用这些预定义的类构建具有标准结构的验证平台。

这就引出了当前最流行的验证方法学:通用验证方法学(Universal Verification Methodology, UVM)是一个以SystemVerilog类库为主体的验证平台开发框架,验证工程师可以利用其可重用组件构建具有标准化层次结构和接口的验证环境。

2 UVM验证平台

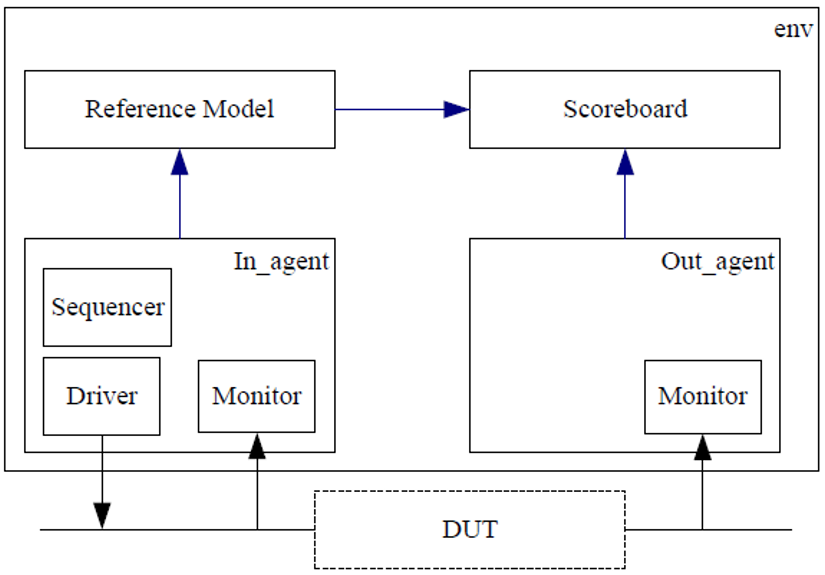

为了实现模块化、可重用和可维护的验证环境,UVM将不同的功能划分到各个组件中。

- DUT: Design Under Test也就是待验证的RTL代码

- env:UVM验证平台的顶层组件,包含了验证平台中常用的组件

- In_agent:代理封装了与接口相关的验证功能

- Driver:负责接收Sequencer产生的transaction,并驱动transaction进入DUT

- Sequencer:负责产生transaction并传输至Driver

- Monitor:负责监视DUT的输入信号,并发送给Reference Model

- Out_agent:代理封装了与接口相关的验证功能

- Monitor:负责监视DUT的输出信号,并发送给Scoreboard

- Reference Model:生成 DUT预期的结果,并发送给Scoreboard

- Scoreboard:比较Reference Model和DUT输出是否一致,并给出比较结果

- In_agent:代理封装了与接口相关的验证功能

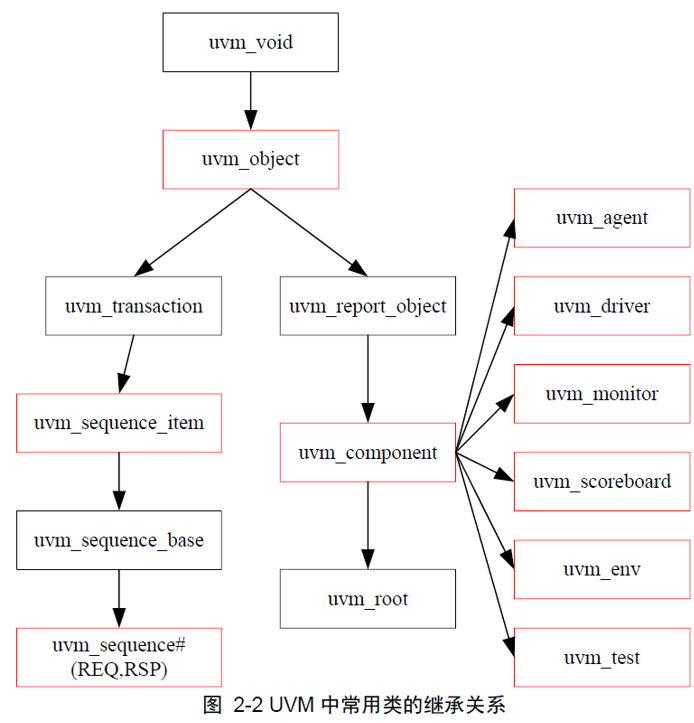

3 UVM类的继承关系

验证平台中的所有component均派生自UVM中的类。例如,env派生自类uvm_env,而类uvm_env继承自类uvm_component。

4 实例

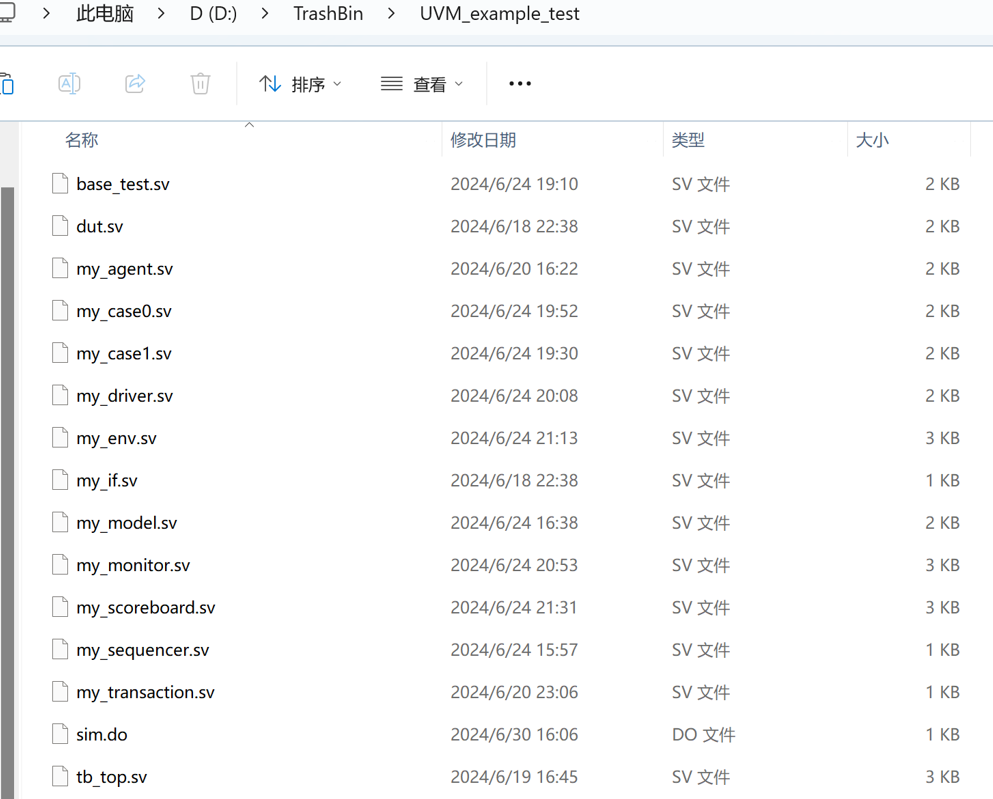

这个链接中的 UVM_example 文件夹包含了一个完整的 UVM 验证平台:https://github.com/Yong12315/UVM

文件夹中的“sim.do”是仿真脚本,其他 SV 文件构成了整个 UVM 验证平台。

4.1 验证环境

Windows 11,QuestaSim 10.6c

4.2 UVM验证流程

1. 创建一个空的文件夹UVM_example_test作为工程文件夹,假设其路径为D:\TrashBin\UVM_example_test。

2. 将UVM_example文件夹中的所有文件复制到UVM_example_test文件夹中。

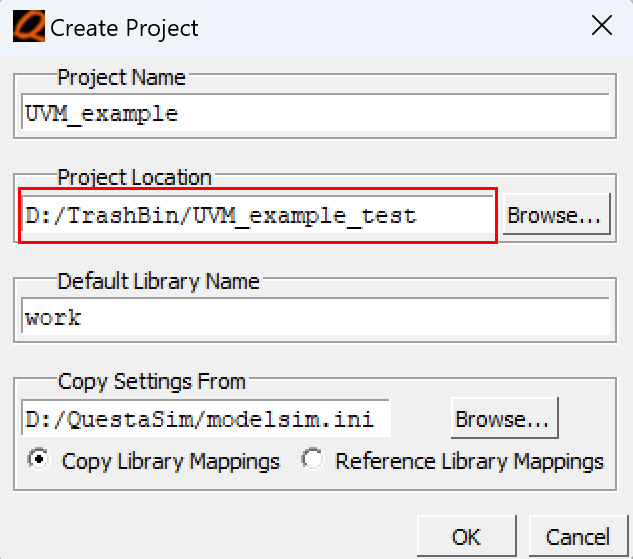

3. 启动QuestaSim,选择File-New-Project,并在Project Location处输入D:\TrashBin\UVM_example_test。

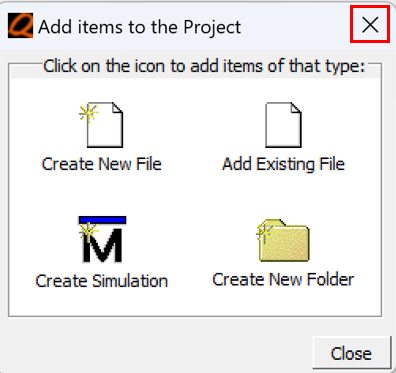

4. 由于在“sim.do”脚本文件中已经定义好了文件的位置,所以不需要再添加文件,直接关闭即可。

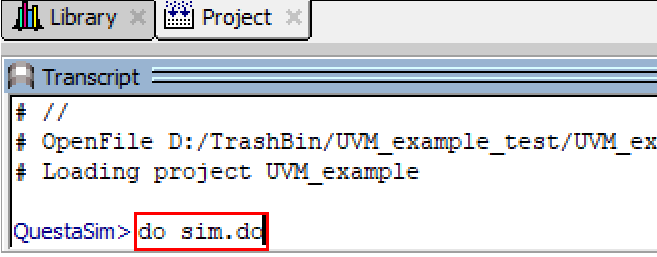

5. 在命令行里输入“do sim.do”,开始UVM验证

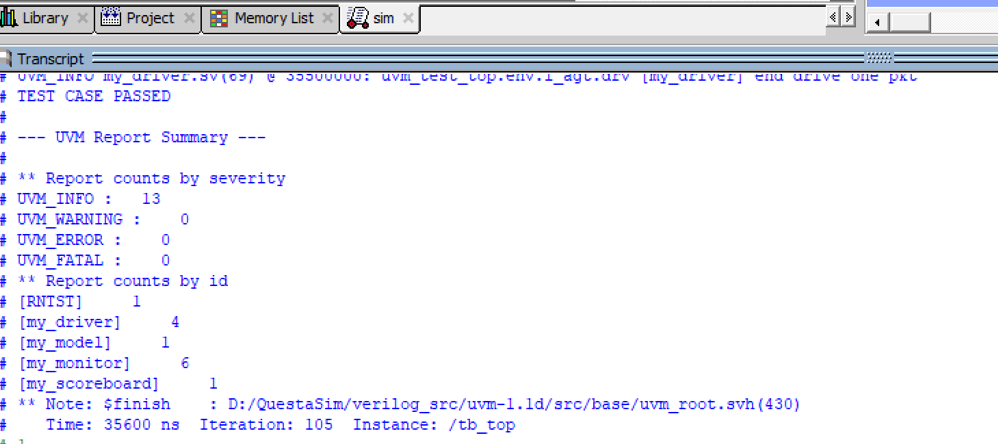

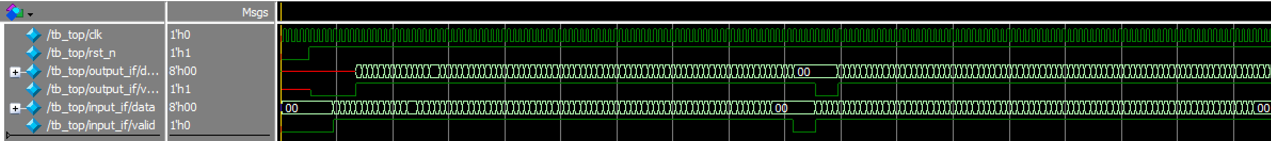

6. 运行之后,可以看到UVM的打印报告和仿真的波形

4.3 小结

通过这个实例,可以大致了解 UVM 验证平台的组成,同时学习如何使用 QuestaSim 进行 UVM 平台的仿真。

5 Reference

1. 《UVM1.1应用指南及源代码分析_20111211版》

Love From China~

Love From China~

文章评论