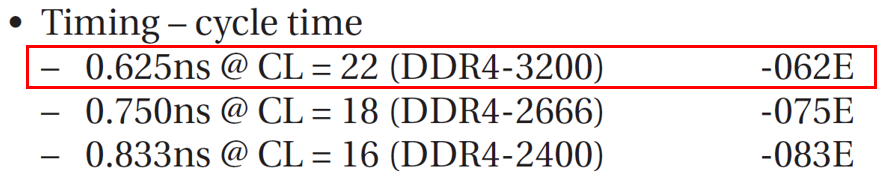

1 背景 使用Zynq平台时,我们往往希望尽量提高PS端程序的运行速度。PS端DDR的数据传输速率对PS端运行速度有显著影响。例如,DDR读写速度慢会减缓处理器在数据读取或写入期间的效率,进而降低整体处理速度。因此,提升PS端DDR的数据传输速率是至关重要的。 2 问题 为了最大限度地提升Zynq MPSoC平台的性能,我们需要深入了解如何配置该平台,以尽量提高DDR的数据传输速率。 3 环境 硬件 主芯片:xczu4ev-sfvc784-2-i;DDR4:MT40A512M16LY-062E 软件 Vivado …

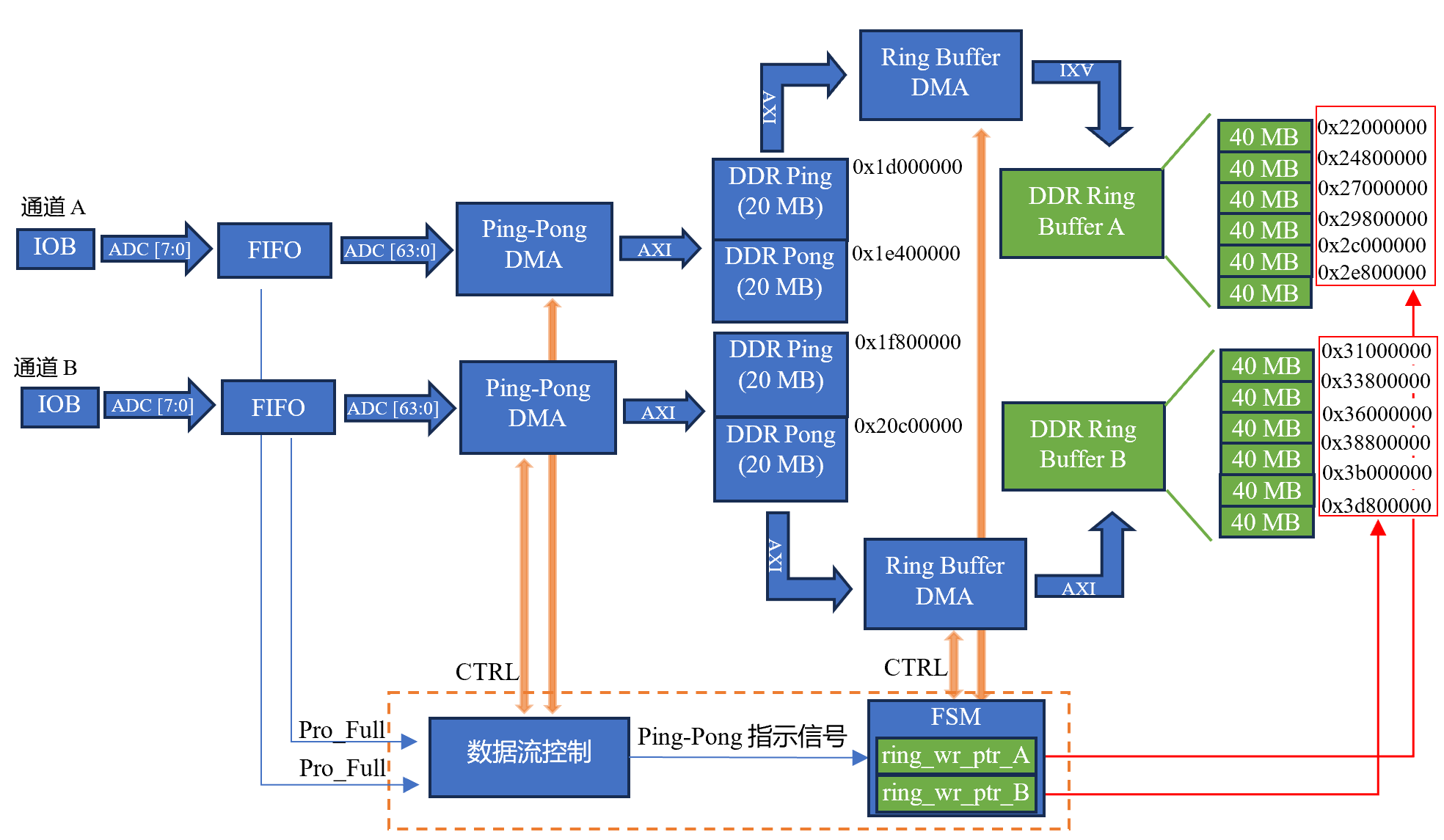

1 需求 1、PL端通过AXI总线将ADC采样得到的每通道40 MB/s的ADC_A和ADC_B两个通道的数据传输至DDR环形缓冲区(Ring Buffer),以便PS端进行读取。 2、提供DDR Ring Buffer的PL写指针,以确保PS端在读取数据时能够避开PL正在写入的DDR地址区域。 2 功能点 1、正确采样每通道40MB/s 的ADC数字信号。 2、将采样得到的ADC数据送入FIFO缓存。 3、将FIFO中的数据搬运到DDR Ping-Pong Buffer缓存。(为将来可能的算法做准备) 4、将DD…

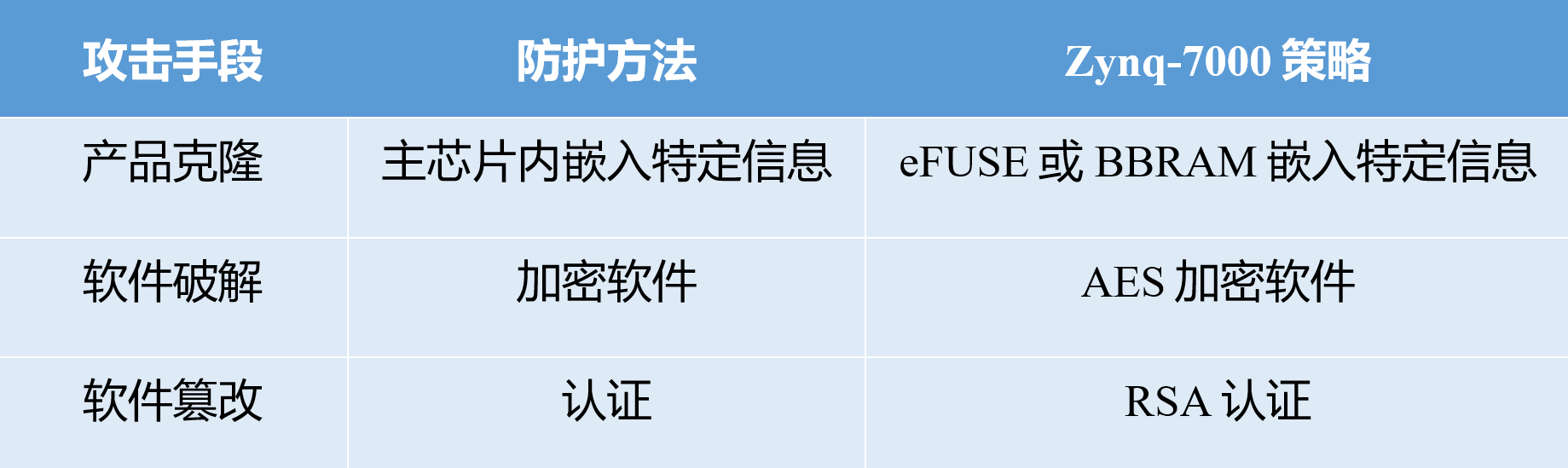

1 背景 当竞争对手获得我们的产品后,可能会采取以下常见行为来侵犯我们的知识产权:产品克隆、软件破解、软件篡改等。这些都是常见的侵权方式。 产品克隆 竞争对手可能通过购买样机,复制其PCB(俗称抄板),购买相应的元器件,并复制非易失性器件(如Flash)中的软件内容来克隆产品。如果这些步骤能让系统启动并执行所有预设功能,竞争对手便可轻松实现产品克隆。 常规芯片策略:在授权的主芯片中嵌入特定信息,系统启动时需与Flash存储器中的程序互相验证。对手若无法复制主芯片的特定信息。若竞争对手不能复制主芯片中的特定信息,那么…