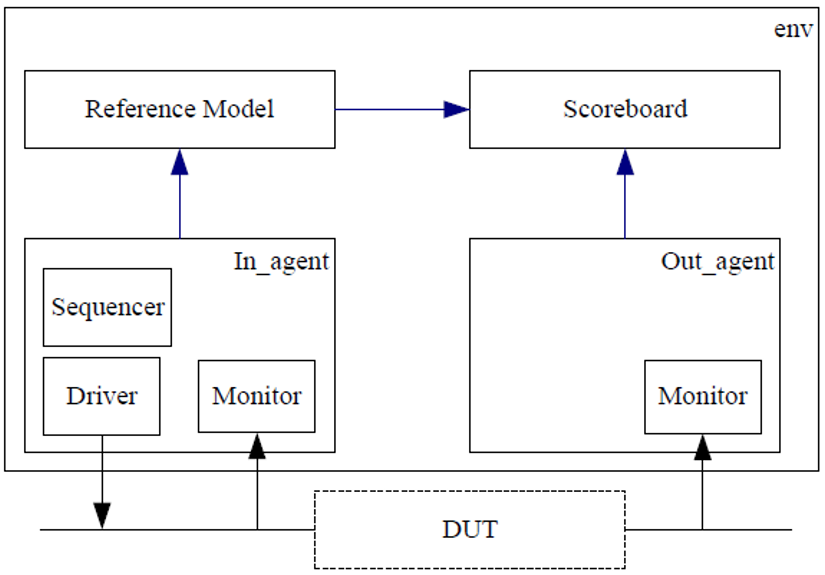

1 背景 如今数字芯片(SoC/ASIC/FPGA)的设计日益复杂,验证工程师的角色也变得越来越重要。有效的验证流程可以在设计初期发现bug,从而显著提升设计的稳定性和正确性。 作为一名FPGA工程师,我发现用Verilog编写的简单testbench已无法满足复杂算法或逻辑的验证需求。Verilog编写的testbench通常非常臃肿且不灵活,不利于代码维护。此外,因为缺乏标准化结构,不同项目通常需要从头搭建验证平台,导致代码难以复用。同时,较差的验证平台结构会增加验证组件之间的耦合,导致对一个组件的修改可能影响…