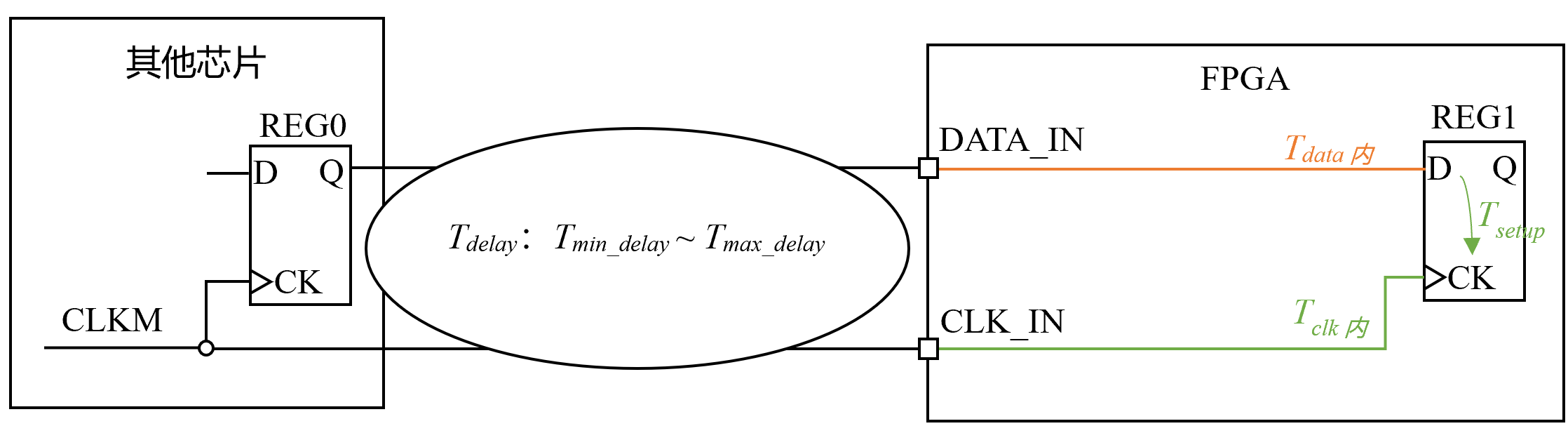

在FPGA设计中,常需与其他芯片通讯。为确保通讯的可靠性,避免产生亚稳态,端口的静态时序分析尤为重要。 1 FPGA输入端口 输入端口的静态时序分析是指验证外部信号在输入至 FPGA 内部第一级寄存器时,其建立时间和保持时间是否满足时序要求。 1.1 原理 1.1.1 建立时间 如图所示,DATA_IN为FPGA的数据输入端口,CLK_IN为相应的时钟输入端口。由于连接FPGA与其他芯片的数据线与时钟线长度不同,以及其他芯片输出的时钟与数据时间存在延迟,因此输入到FPGA的DATA_IN需要比CLK_IN延迟Tde…

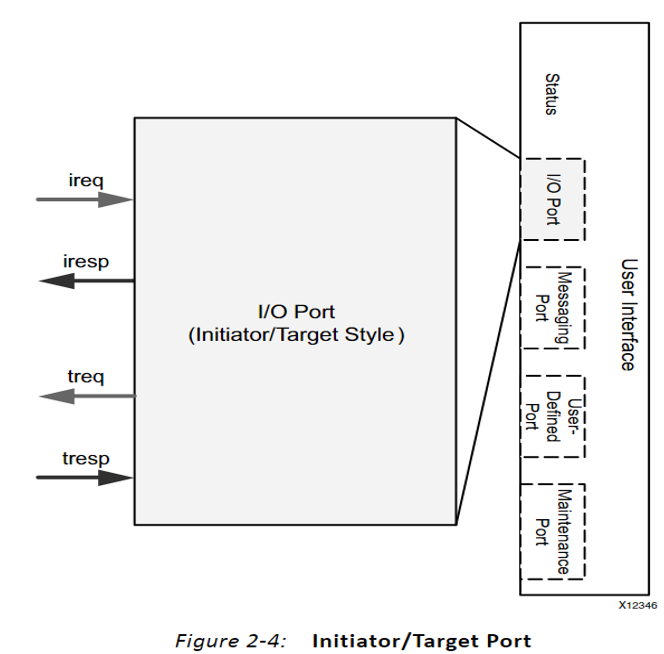

1 背景 在用户使用Xilinx SRIO Gen2 IP时,最关注的就是User Interface。因为用户只需理解User Interface,就能利用SRIO Gen2 IP实现数据的高速传输,而不需要关注RapidIO协议的过多细节。User Interface包含I/O端口集和三个可选端口。其中,任何支持的I/O事务(例如NWRITEs、NWRITE_Rs、SWRITEs、NREADs、RESPONSEs和DOORBELL)都通过I/O端口进行发送或接收。 I/O端口可以配置为两种模式:Condense…

1 背景 在Xilinx AXI 1G/2.5G Ethernet Subsystem IP中,使用了双通道AXI Stream接口设计,实现了数据流与控制流/状态流的分离。数据流用于传输以太网报文数据,控制流用于传输TX标志信息和校验指示信息,状态流用于传输报文的目的MAC地址和状态等信息。 IP示意图: 2 解析 2.1 TX Stream 如图所示,TX_data的ready信号需要等到TX_control的控制流信息被完全接收后才能拉高。因此,对于每一帧报文,IP必须先接收控制流信息,然后才能接收数据流。 …

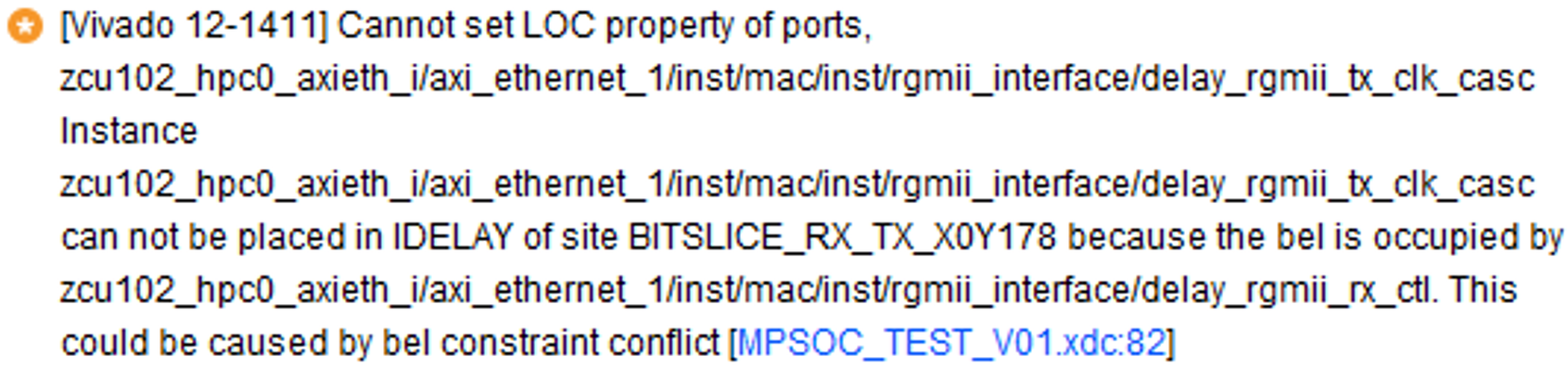

1 背景 在FPGA的高速接口应用中,接口时序常常要求非常严格。因此,经常会利用IOB(I/O Block)中的IODelay资源对端口信号进行延时调整。单个IODelay所能提供的延时是有限的;当需要较长延时时,可以采用IODelay级联以实现更长时间的延时。 2 问题 在以太网工程应用中,为了对输出时钟TXC端口进行延时,采用了ODELAY3和IDELAY3级联。然而,在绑定I/O端口时,遇到了报错。 3 分析 由报错可知,TXC端口所需的IDELAY3的位置(BITSLICE_RX_TX_X0Y178)已被R…