1 需求

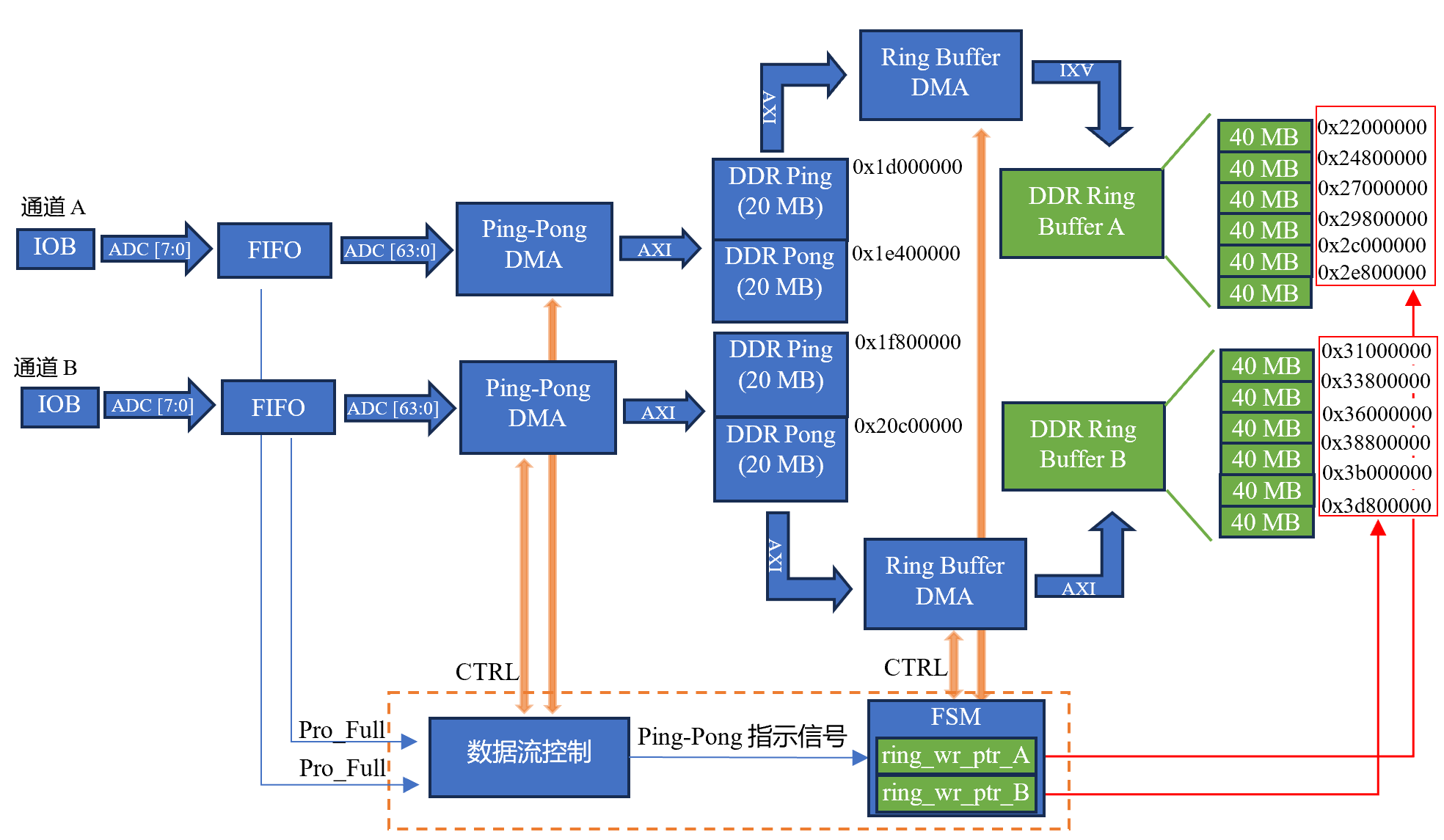

1、PL端通过AXI总线将ADC采样得到的每通道40 MB/s的ADC_A和ADC_B两个通道的数据传输至DDR环形缓冲区(Ring Buffer),以便PS端进行读取。

2、提供DDR Ring Buffer的PL写指针,以确保PS端在读取数据时能够避开PL正在写入的DDR地址区域。

2 功能点

1、正确采样每通道40MB/s 的ADC数字信号。

2、将采样得到的ADC数据送入FIFO缓存。

3、将FIFO中的数据搬运到DDR Ping-Pong Buffer缓存。(为将来可能的算法做准备)

4、将DDR Ping-Pong Buffer中的数据搬运到DDR Ring Buffer中,供PS端读取。

5、ring_wr_ptr寄存器用作DDR Ring Buffer的写指针,指示PL当前写入的DDR地址区域。这保障了PS端在读取数据时避免与PL正在写入的40 MB DDR地址区域冲突。

3 详细设计

3.1 设计框图

3.2 IOB采样

通过I/O Block内的寄存器对输入的ADC数字信号进行采样,确保从端口输入至寄存器的采样延迟是固定的,从而保证数据采样的准确性。然后将采样得到的信号输出到FIFO。

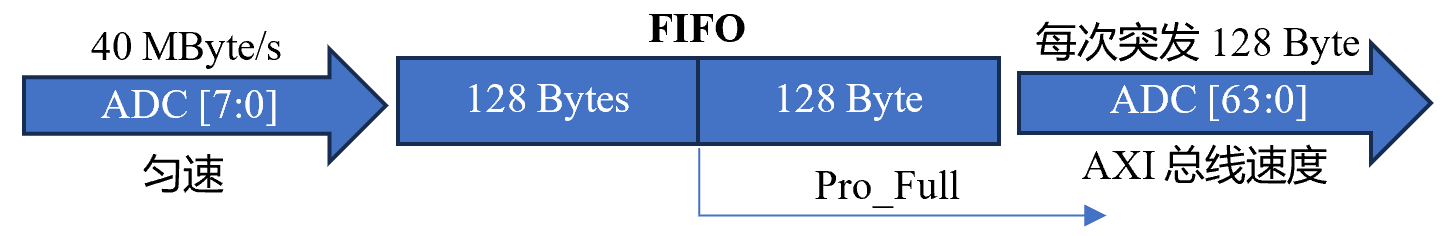

3.3 FIFO设计

1、Ping-Pong搬运模块每次从FIFO突发搬运128 Bytes数据,因此FIFO至少要缓存128 Bytes数据。

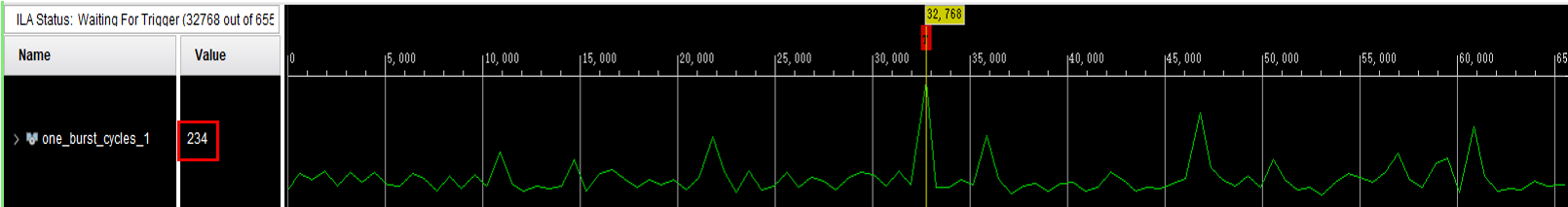

2、当AXI总线繁忙时,FIFO的突发搬运速率会发生波动。因此,FIFO的设计必须确保即使在突发搬运速率最慢的情况下,也能防止FIFO写入数据的溢出。实测发现,从FIFO突发搬运128 Bytes数据最慢需要Ncycles = 234个时钟周期。

由于FIFO读出时钟为200 MHz,时钟周期为TC = 5ns。

FIFO最慢一次突发搬运的时间Tone_burst:

Tone_burst= Ncycles× TC=234×5ns=1170 ns

这段时间写入FIFO的数据Din:

Din=40 MByte/s × Tone_burst = 47 Bytes

为了防止写入数据Din的丢失,FIFO大小至少要为 128 Bytes + 47 Bytes = 175 Bytes。

3、FIFO突发搬运的过程中,可能会因总线繁忙等原因导致搬运速度变慢。为了防止这种情况下数据的溢出,后续数据 < 128 Bytes时,应能够暂存在FIFO中以保持数据的完整性。因此,FIFO最终采用背靠背设计,128 Bytes × 2 = 256 Bytes。

综上:FIFO的容量设计为256 Bytes,采用背靠背设计。当其中的数据量达到128 Bytes时,将Pro_Full信号置高,输出到数据流控制模块。

3.4 数据流控制模块

1、数据流控制模块根据Pro_Full信号判断FIFO中是否有128 bytes数据。

2、当FIFO中的数据量达到128 Bytes时,CTRL信号使得Ping-Pong搬运模块开始数据搬运。CTRL信号还会指定数据搬运的目标地址,使得Ping-Pong搬运模块能够交替地将FIFO中的数据搬运到DDR Ping和DDR Pong缓冲区中。

3、输出Ping-Pong指示信号到FSM模块,标明搬运的数据是进入DDR Ping还是DDR Pong。

3.5 Ping-Pong DMA 模块

Ping-Pong DMA模块根据数据流控制模块的信号CTRL,会从FIFO中取出128 Bytes的数据,并通过AXI总线将这些数据搬运至DDR Ping 或DDR Pong。

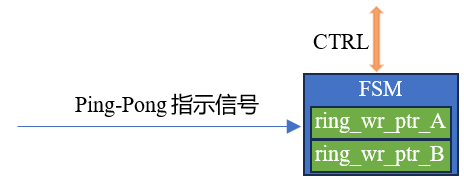

3.6 FSM设计

1、根据Ping-Pong指示信号,判断当前DDR Ping和DDR Pong哪个处于非写入状态。

2、CTRL信号负责控制Ring Buffer搬运模块,使得Ring Buffer搬运模块搬运将非写入状态的DDR Ping或DDR Pong中的数据搬运到DDR Ring Buffer中。在搬运过程中,CTRL信号提供给Ring Buffer搬运模块的源地址和目的地址。目的地址每隔半秒递增,实现每半秒将Ping-Pong Buffer中的数据搬运到DDR Ring Buffer中。

3、PS端能够访问ring_wr_ptr_A和ring_wr_ptr_B寄存器。其中,ring_wr_ptr_A是PL端A通道当前写入的DDR Ring Buffer A的写指针,指向正写入的40 MB DDR地址空间的起始地址。同样,ring_wr_ptr_B是PL端B通道当前写入的DDR Ring Buffer B的写指针,也指向相应40 MB DDR地址空间的起始地址。

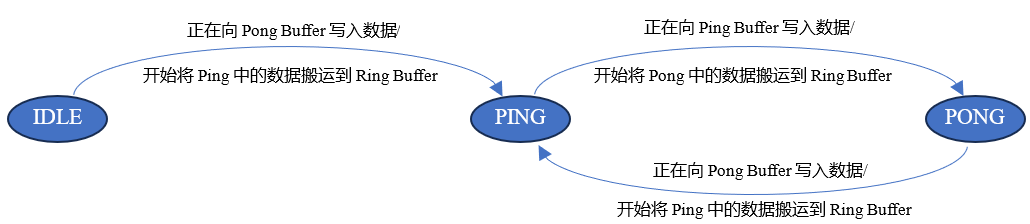

状态机图:

IDLE:空闲状态。

PING: DDR Pong正在写入,DDR Ping数据搬运到Ring Buffer。

PONG: DDR Ping正在写入,DDR Pong数据搬运到Ring Buffer。每次Pong搬运结束后,时间计数器加1,当计数器值达到5时,将其重置为零。计数器指示正在写入第几秒的数据。

3.7 Ring Buffer DMA模块

Ring Buffer搬运模块受FSM的控制信号CTRL控制,按照该信号指示从DDR Ping和DDR Pong交替搬运数据到DDR Ring Buffer中。每隔半秒,该模块从DDR Ping或DDR Pong搬运单通道20Mbyte数据至DDR Ring Buffer。

Love From China~

Love From China~

文章评论

通过I-O Block内的寄存器对ADC数字信号进行采样,确保采样延迟固定,从而保证数据准确性。FIFO采用背靠背设计,容量为256 Bytes,防止数据溢出。Ping-Pong搬运模块根据CTRL信号交替将数据搬运到DDR Ping和DDR Pong缓冲区。Ring Buffer搬运模块每半秒将数据搬运到DDR Ring Buffer中,确保数据流的高效处理。如何确保在总线繁忙时,FIFO中的数据不会丢失? Given the growing economic instability due to the events in the Middle East, many businesses are looking for guaranteed fast and secure payment solutions. Recently, I came across <a href="https://libersave.com/de/">LiberSave</a> (LS) — they promise instant bank transfers with no chargebacks or card verification. It says integration takes 5 minutes and is already being tested in Israel and the UAE. Has anyone actually checked how this works in crisis conditions?