在FPGA设计中,常需与其他芯片通讯。为确保通讯的可靠性,避免产生亚稳态,端口的静态时序分析尤为重要。

1 FPGA输入端口

输入端口的静态时序分析是指验证外部信号在输入至 FPGA 内部第一级寄存器时,其建立时间和保持时间是否满足时序要求。

1.1 原理

1.1.1 建立时间

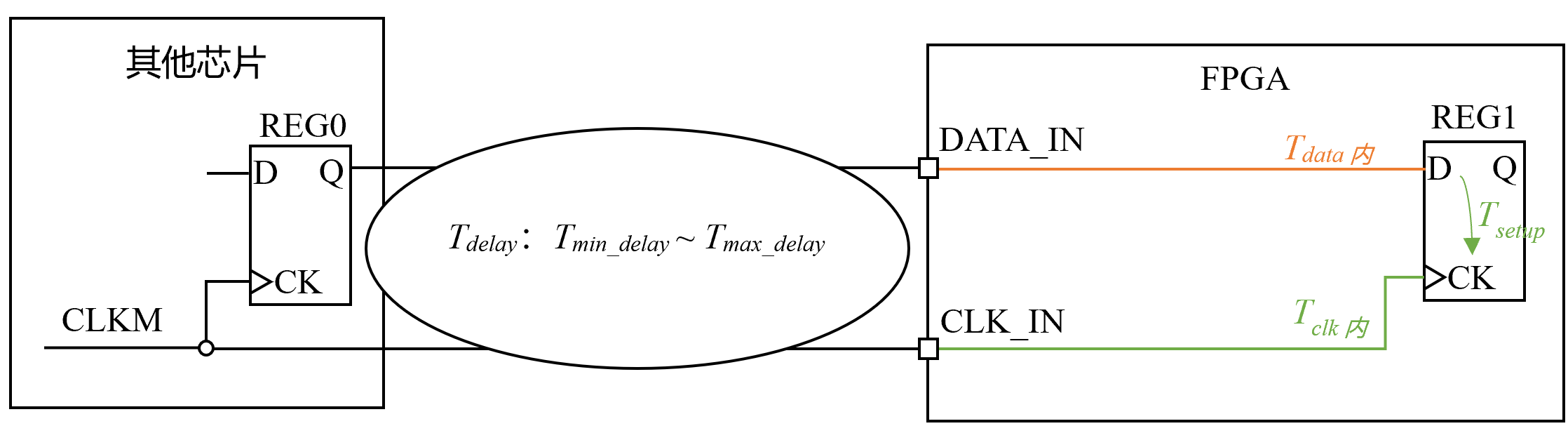

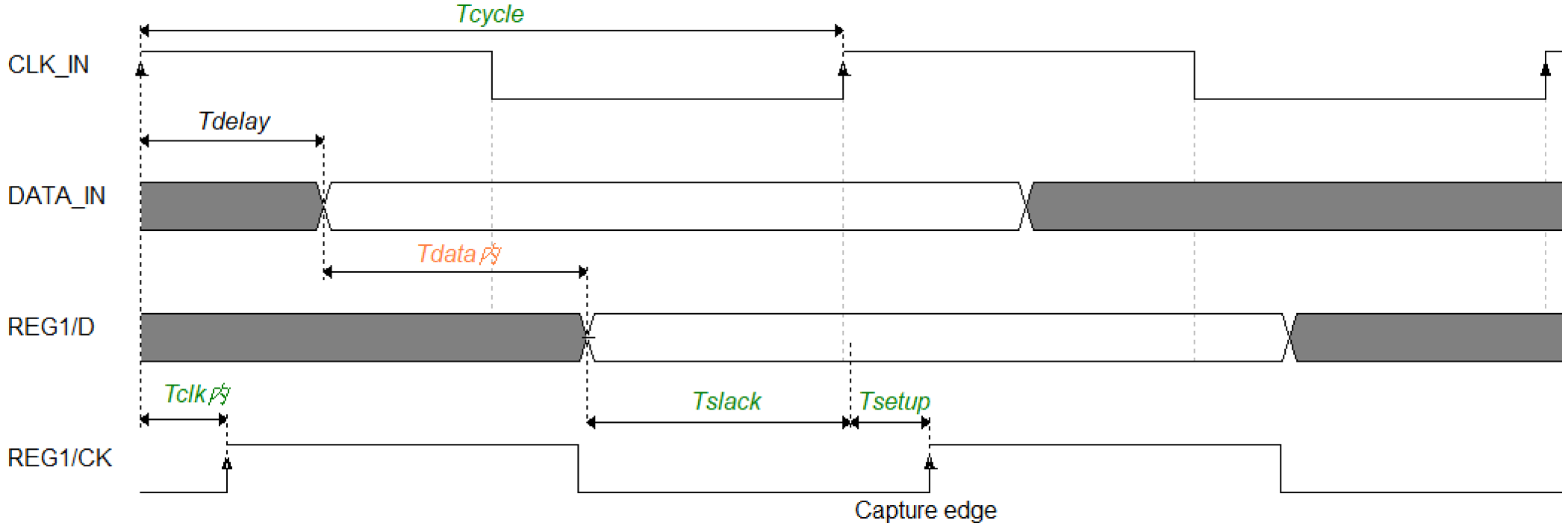

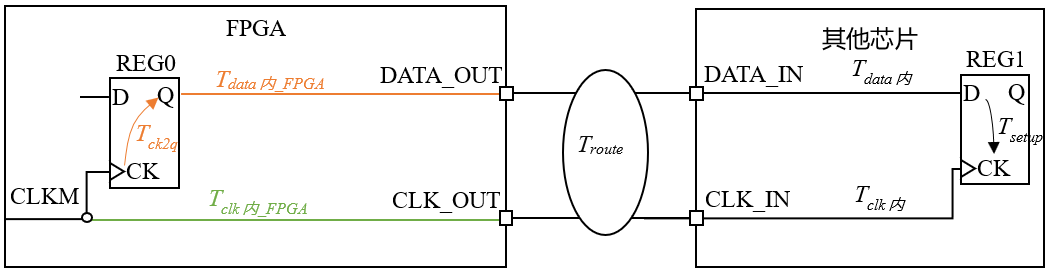

如图所示,DATA_IN为FPGA的数据输入端口,CLK_IN为相应的时钟输入端口。由于连接FPGA与其他芯片的数据线与时钟线长度不同,以及其他芯片输出的时钟与数据时间存在延迟,因此输入到FPGA的DATA_IN需要比CLK_IN延迟Tdelay时间。例如,如果其他芯片的引脚输出数据相对于时钟延迟Tchip_delay,且连接FPGA与其他芯片的走线导致数据线相对于时钟线延迟Troute_delay,则Tdelay = Tchip_delay + Troute_delay。

如果时钟到达CLK_IN端口的时间设定为0,则数据到达DATA_IN端口的时间为Tdelay。数据到达FPGA内部的捕获寄存器REG1/D的时间为Tdelay+ Tdata内,而捕获时钟到达捕获寄存器REG1/CK的时间为Tclk内+ Tcycle。要求数据到达REG1的时间比时钟到达REG1的时间至少早Tsetup,以确保数据的正确捕获。因此,对于FPGA的建立时间检查,需满足以下公式:

![]()

对于像Vivado这样的FPGA设计软件,上述公式中只有Tdelay是未知的因此,需要通过时序约束来指定Tdelay。为了保证在最差时序条件下也能满足建立时间,当Tdelay为其最大值Tmax_delay时,上述公式也应成立。因此,应如下设定输入端口的建立时间约束,以便软件能够分析输入端口的建立时间:

- create_clock -period Tcycle -name CLK_IN -waveform {0 Tcycle / 2} [get_ports CLK_IN]

- set_input_delay -clock CLK_IN -max Tmax_delay [get_ports DATA_IN]

1.1.2 保持时间

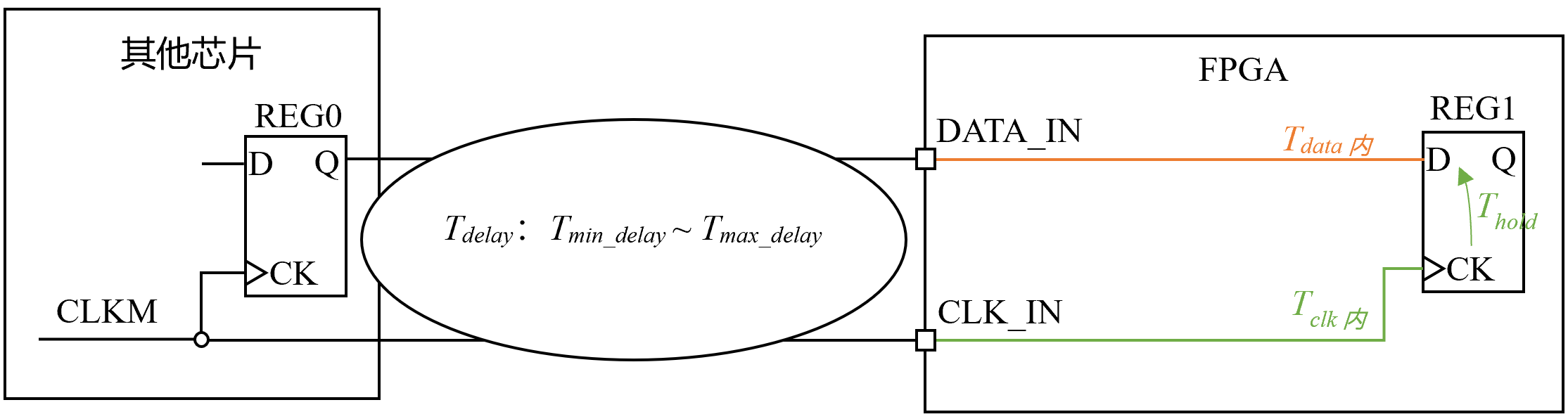

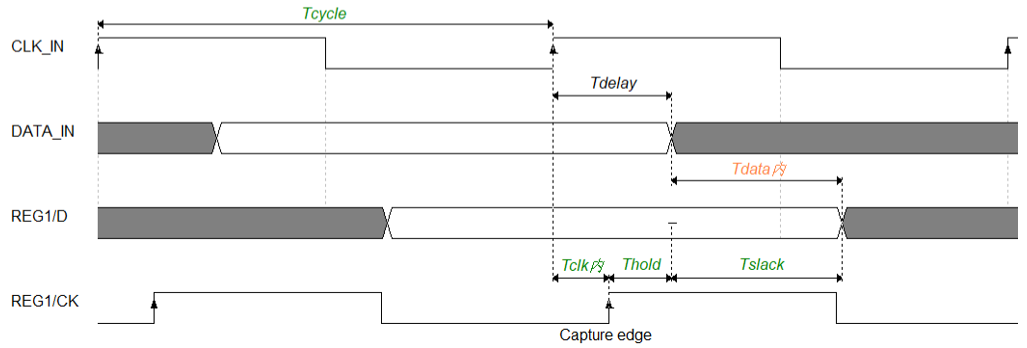

如果时钟到达CLK_IN端口的时间设定为0,则DATA_IN端口的数据在Tdelay时刻发生变化。FPGA内部的捕获寄存器REG1/D的数据在Tdelay + Tdata内时刻发生变化,而捕获寄存器REG1/CK的时钟将在Tclk内时刻捕获REG1/D的数据。为确保数据正确捕获,要求数据在被REG1的时钟捕获时至少保持Thold时间稳定不变。因此,对于FPGA的保持时间检查,需满足以下公式:

![]()

对于像Vivado这样的FPGA设计软件,上述公式中只有Tdelay是未知的。因此,需要通过时序约束来指定Tdelay。为了保证在最差时序条件下也能满足保持时间,当Tdelay为其最小值Tmin_delay时,上述公式也应成立。因此,应如下设定输入端口的保持时间约束,以便软件能够分析输入端口的保持时间:

- create_clock -period Tcycle -name CLK_IN -waveform {0 Tcycle / 2} [get_ports CLK_IN]

- set_input_delay -clock CLK_IN -min Tmin_delay [get_ports DATA_IN]

1.2 示例

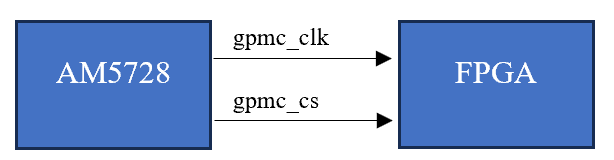

以 AM5728 芯片与 FPGA 通过 GPMC 接口通信中的片选信号 gpmc_cs 为例:

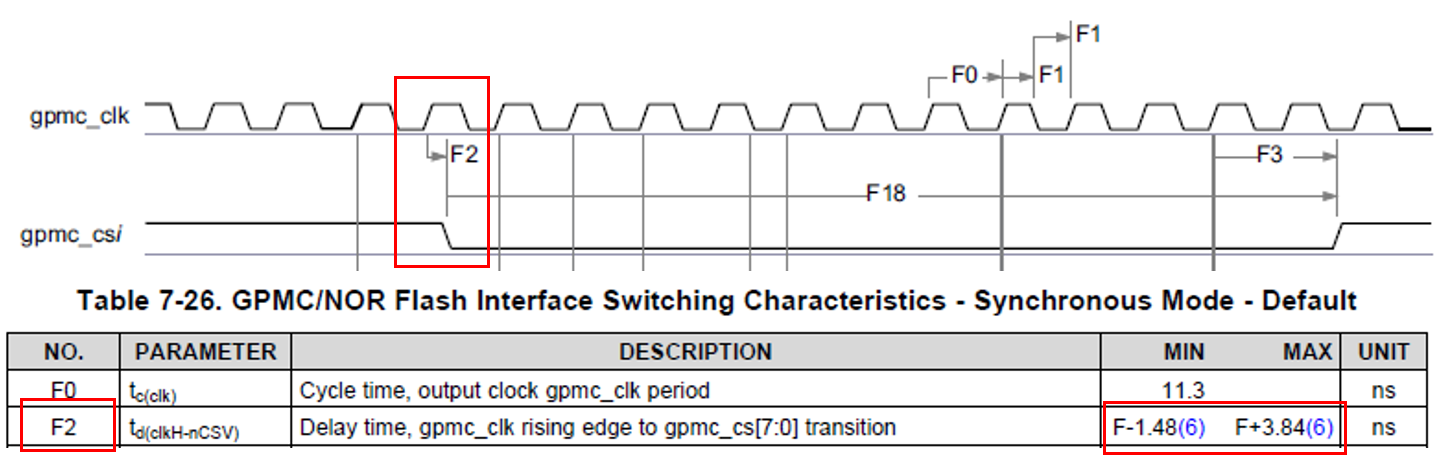

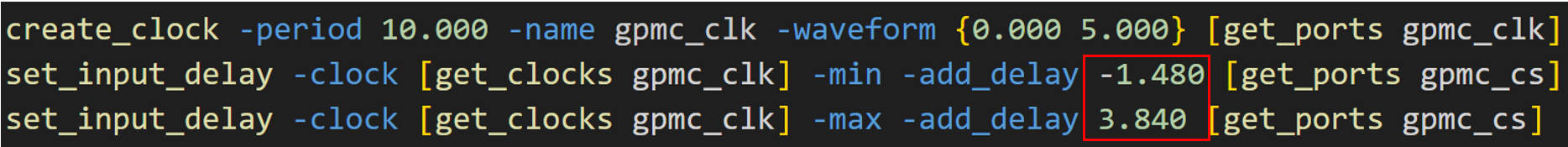

查阅AM5728的芯片手册可以得到芯片片选信号gpmc_cs与时钟gpmc_clk的时序关系:

gpmc_clk为100MHz。gpmc_cs信号相对于时钟 gpmc_clk延后的时间为-1.48ns ~ 3.84ns。假设PCB信号线等长时间差很小,可以忽略不计,所以gpmc_cs信号相对于时钟gpmc_clk延后-1.48ns ~ 3.84ns到达FPGA。

因此,在 Vivado 的 XDC 中可按如下方式对 gpmc_cs 设置输入延迟约束:

2 FPGA输出端口

FPGA 输出端口的静态时序分析是指验证信号从 FPGA 内部最后一级寄存器传输到输出端口时,能否在规定时间内稳定输出到 FPGA 端口,从而满足外部器件的建立时间和保持时间的时序要求。

2.1 原理

2.1.1 建立时间

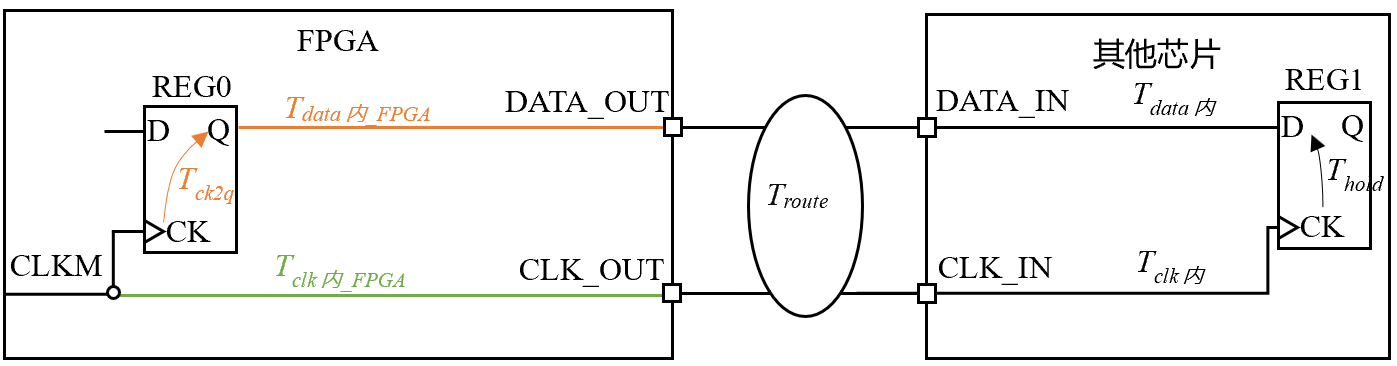

如图所示,DATA_OUT为FPGA的数据输出端口,CLK_OUT为相应的时钟输出端口。假设FPGA输出的数据比时钟提前TFPGA,PCB上时钟和数据线做了等长处理(Troute = 0),那么输入其他芯片的数据要比时钟提前TFPGA。为了满足其他芯片的建立时间,输入的数据通常需要比时钟提前至少(Tdata内+Tsetup – Tclk_内)的时间稳定,这个时间芯片手册一般会标出。因此,当TFPGA≥(Tdata内+Tsetup – Tclk_内)时,能够满足其他芯片的建立时间。

对于像Vivado这样的FPGA设计软件,需要明确指出TFPGA,软件才会分析输出端口的数据能否比时钟提前TFPGA的时间稳定下来。需要通过时序约束“set_output_delay”来指定Tdelay。因此,应如下设定输出端口的建立时间约束,以便软件能够分析输出端口的时序:

- set_output_delay -clock CLKM -max TFPGA [get_ports DATA_OUT]

2.1.2 保持时间

如图所示,DATA_OUT为FPGA的数据输出端口,CLK_OUT为相应的时钟输出端口。假设FPGA输出的数据比时钟提前TFPGA,PCB上时钟和数据线做了等长处理(Troute = 0),那么输入其他芯片的数据要比时钟延后-TFPGA。为了满足其他芯片的保持时间,输入的数据通常需要比时钟延后至少(Tclk + Thold – Tdata内)的时间变化,这个时间芯片手册一般会标出。因此,当TFPGA ≤ -(Tclk + Thold – Tdata内)时,能够满足其他芯片的建立时间。

对于像Vivado这样的FPGA设计软件,需要明确指出TFPGA,软件才会分析输出端口的数据能否比时钟延后TFPGA的时间变化。因此,应如下设定输出端口的保持时间约束,以便软件能够分析输出端口的时序:

- set_output_delay -clock CLKM -min TFPGA [get_ports DATA_OUT]

2.1 示例

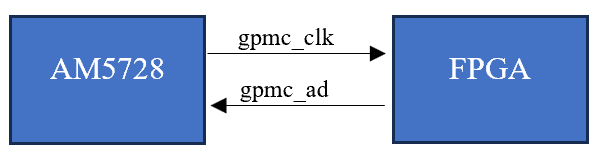

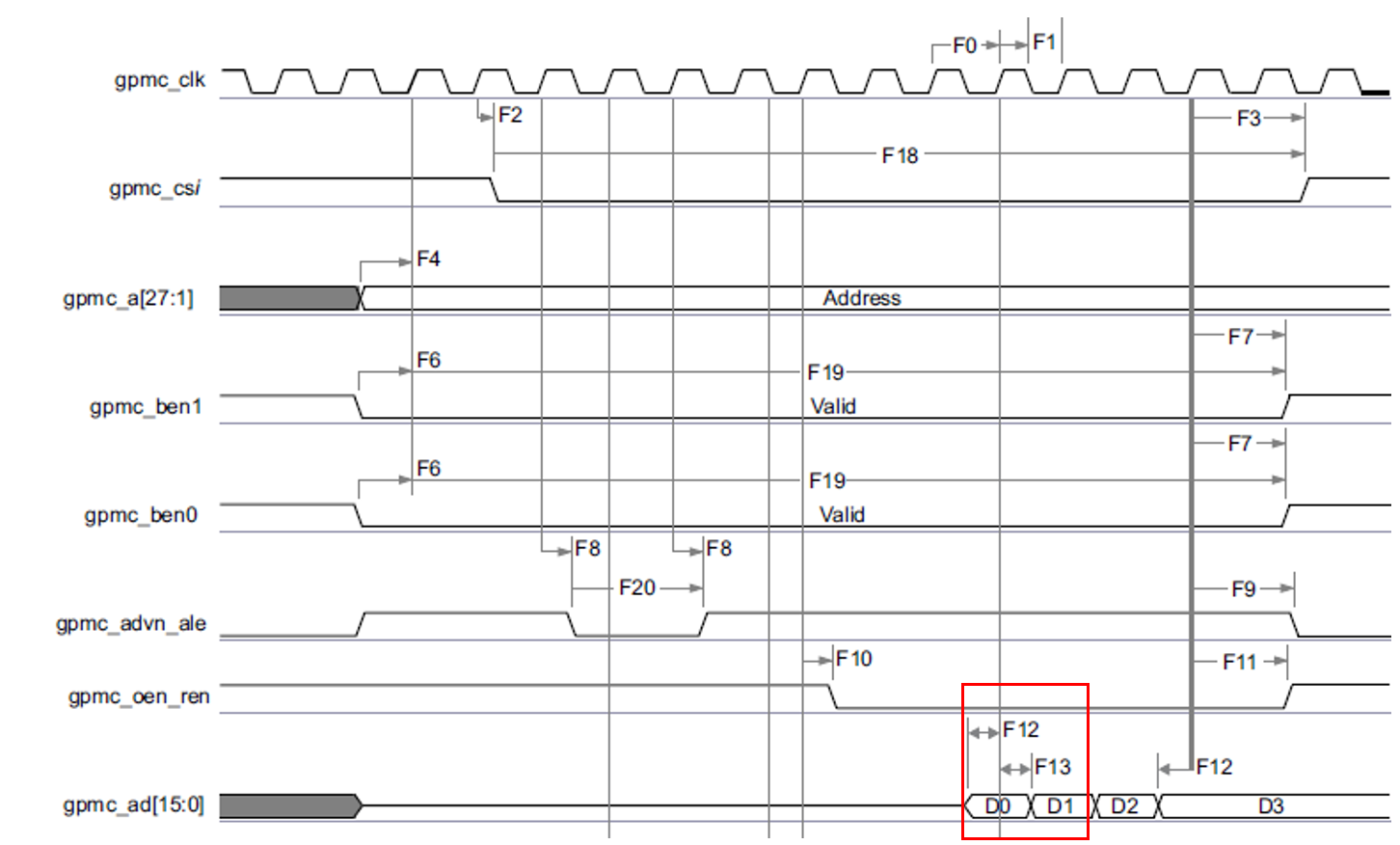

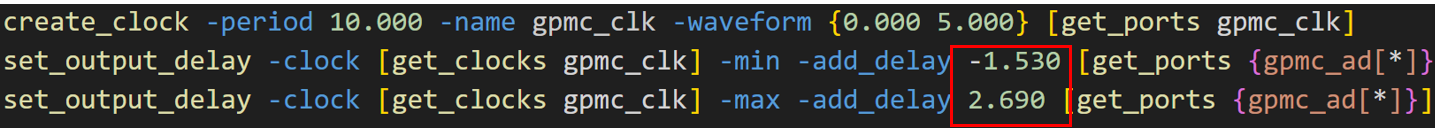

以 AM5728 芯片与 FPGA 通过 GPMC 接口通信中的数据信号 gpmc_ad为例:

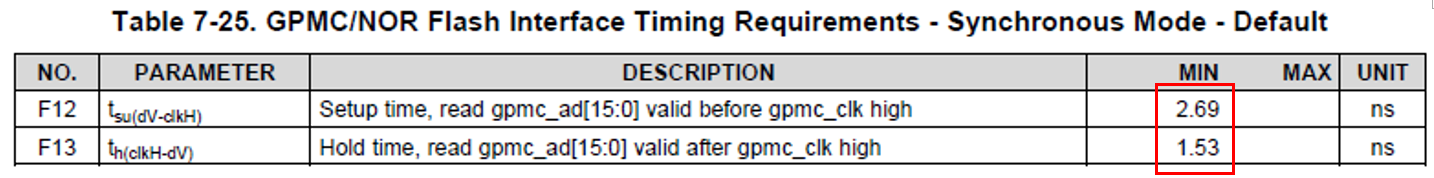

查阅AM5728的芯片手册可以得到芯片数据信号 gpmc_ad与时钟gpmc_clk的时序关系。

gpmc_clk为100MHz。gpmc_ad信号相对于时钟 gpmc_clk上升沿要提前2.69ns稳定,并且gpmc_ad信号在时钟 gpmc_clk上升沿之后1.53ns才能变化。

因此,在 Vivado 的 XDC 中可按如下方式对 gpmc_ad 设置输出延迟约束:

3 REFERENCE

1. https://blog.csdn.net/aaaaaaaa585/article/details/118862049

2. https://blog.csdn.net/aaaaaaaa585/article/details/118859268

3. Rakesh Chadha, J. Bhasker (auth.) - Static Timing Analysis for Nanometer Designs_ A Practical Approach (2009, Springer) [10.1007_978-0-387-93820-2]

Love From China~

Love From China~

文章评论